ARM调试接口——PART B2 调试端口(DP)参考信息

引言

在本文中,主要介绍(翻译)ARM调试接口中调试端口(DP)的具体参考信息。

水平有限,难免存在出错的地方。具体还请查阅手册。

作者注:本文介绍的是ADIv6版本的DP。ADIv6版本的DP与ADIv5的DP存在较大区别,且不完全向前兼容。如果您需要ADIv5的相关信息,请不要继续阅读本文。2020年的Cortex-M55及以后的架构使用到了ADIv6。

本文一共包含以下几个部分:

- 调试端口(DP)架构版本

- DP寄存器的完整说明

- 系统与调试电源的控制行为

- 调试复位的控制行为

- 文中出现的术语、缩写

调试端口(DP)架构版本

在本节中,主要介绍调试端口(DP)架构版本的概念,此外还介绍了DPv3版本的DP寄存器。本节中包含以下两个小节:

- DP架构版本摘要

- DPv3的地址映射(address map)

JTAG-DP和SW-DP之间的一个重要区别是寄存器的访问方式不同。因此,寄存器描述表格中将不会包含寄存器的地址信息,对于不同类型的DP,我们会将地址信息放在每个具体寄存器描述的开头部分。

DP架构的某些地方由数据链路定义(DATA LINK DEFINED),它们将在下面这些章节中讲述(笔者注:非本篇文章内容):

- 章节B3: JTAG调试端口(JTAG-DP)

- 章节B4: SW调试端口(SW-DP)

- 章节B5: SW/JTAG调试端口(SWJ-DP)

DP架构版本摘要

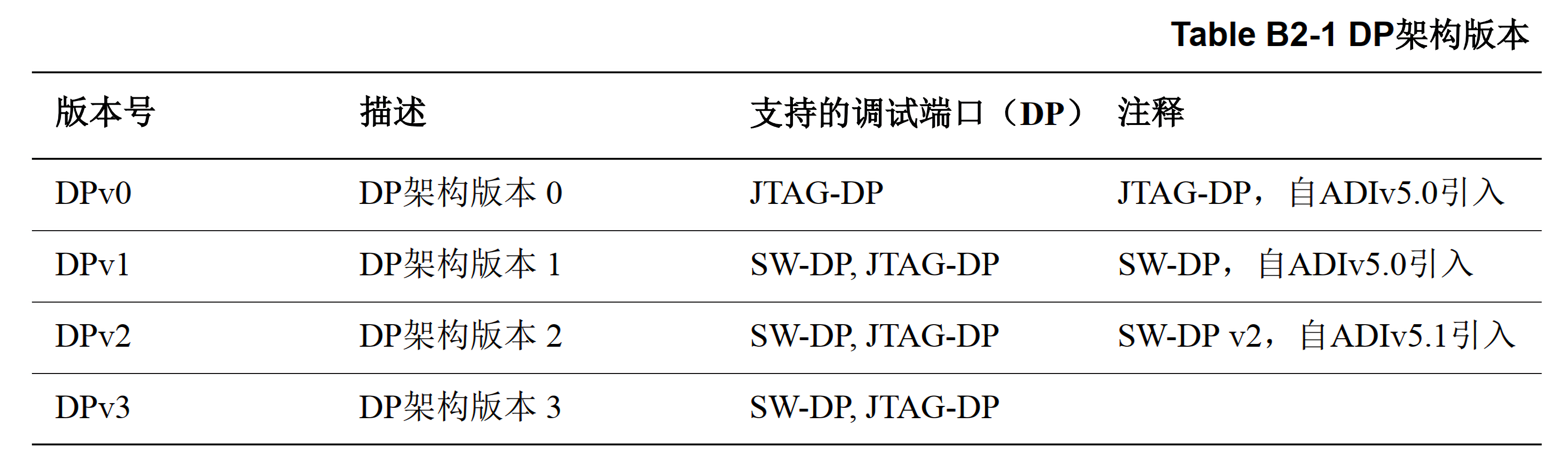

所有的ARM调试接口(ADI)均包含单个的DP,该DP符合某个DP架构版本。表B2-1列出了这些DP版本:

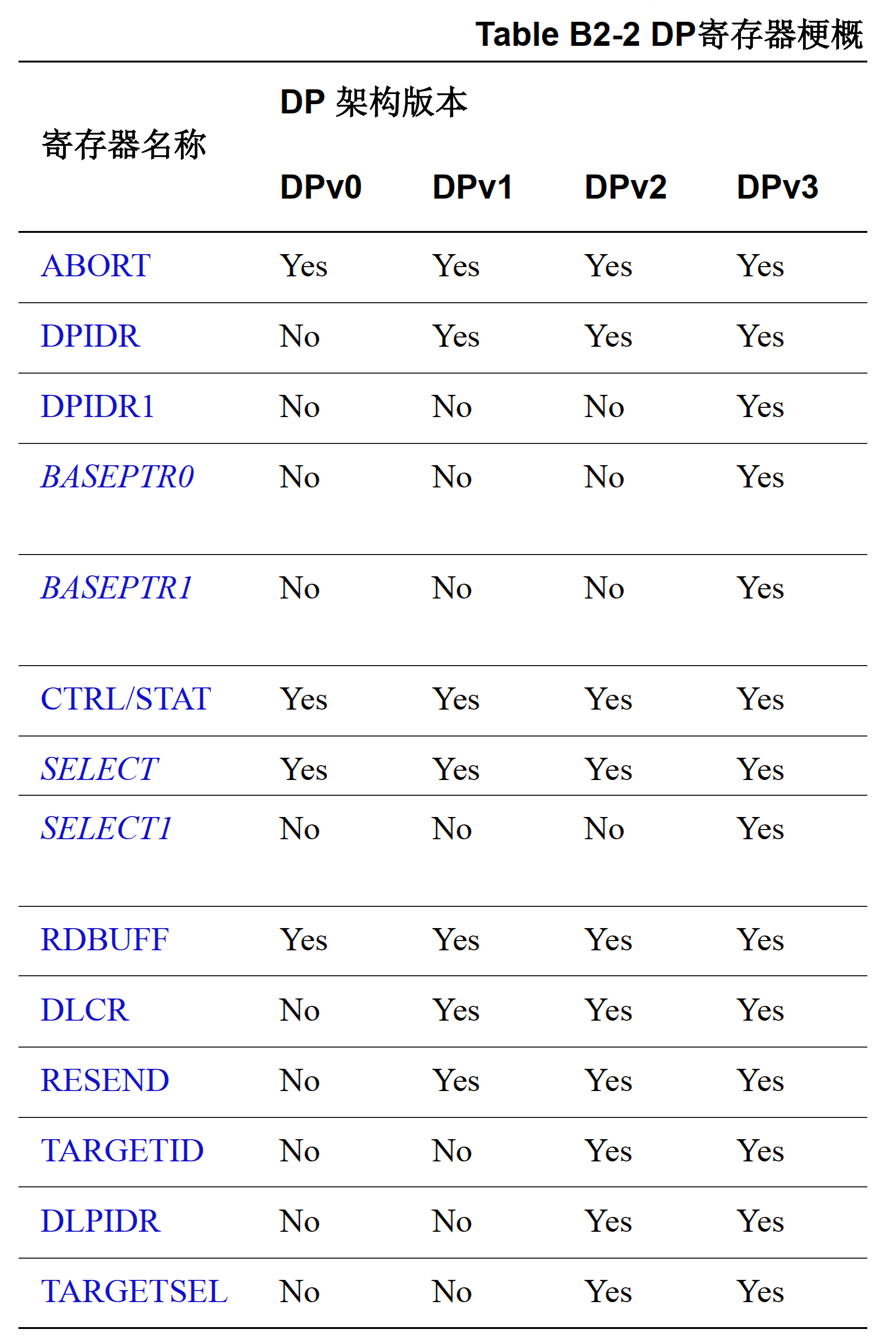

尽管DP架构的版本不同,但是它们的寄存器集合大体上是类似的,表B2-2展示了各个版本的DP架构是否包含这些寄存器。

有关寄存器在特定的架构版本中的实现方式、实现方式是否由数据链路定义(DATA LINK DEFINED),详见下文

DP寄存器描述一节。

DPv3地址映射

DPv3对DP寄存器映射做出了以下修改:

- 修改

DPIDR以引入DPv3版本。 - 扩展了

SELECT寄存器,并引进SELECT1寄存器以支持64位系统地址。 - 引入对JTAG DP协议v1版本的支持。

引入对以下寄存器的定义:

- 调试端口鉴别寄存器1(Debug Port Identification Register 1, DPIDR1)。

- 基址寄存器(Base Pointer Register, BASEPTR0-BASEPTR1)。

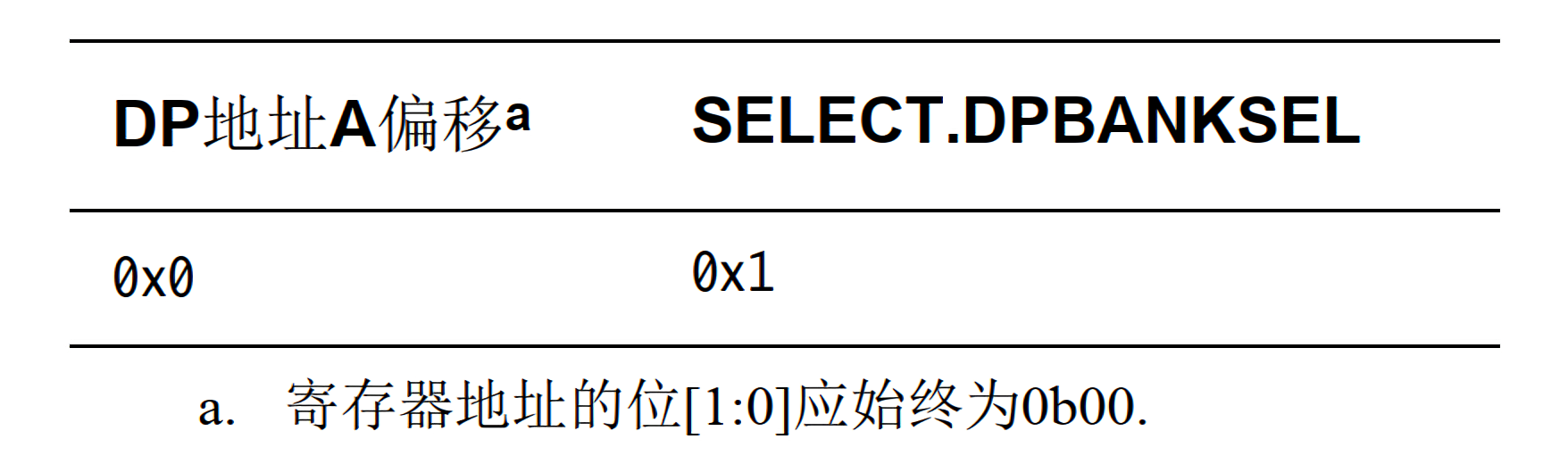

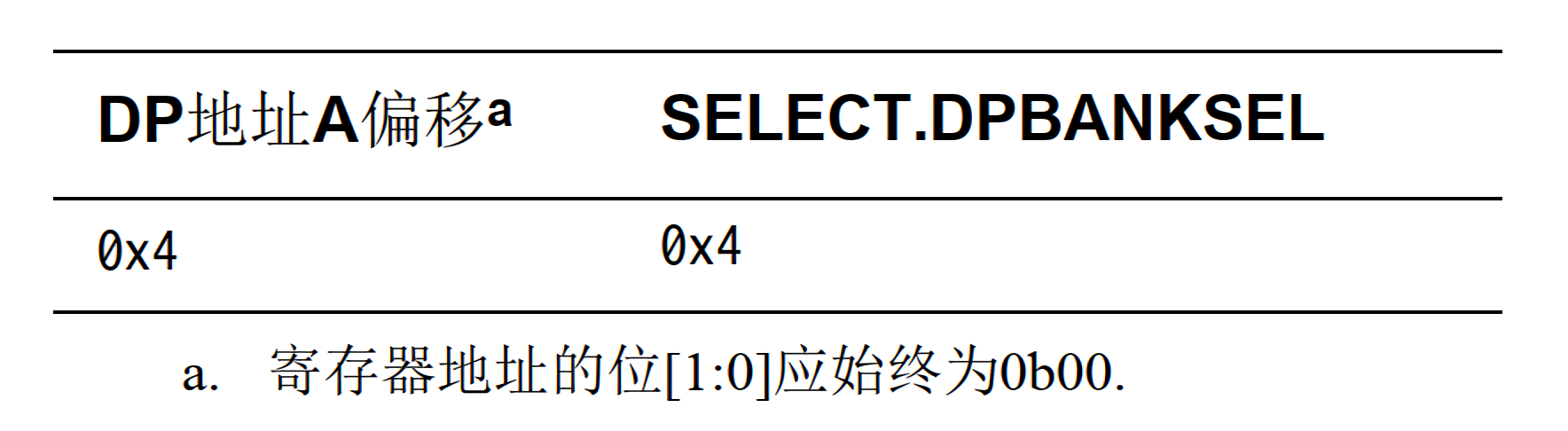

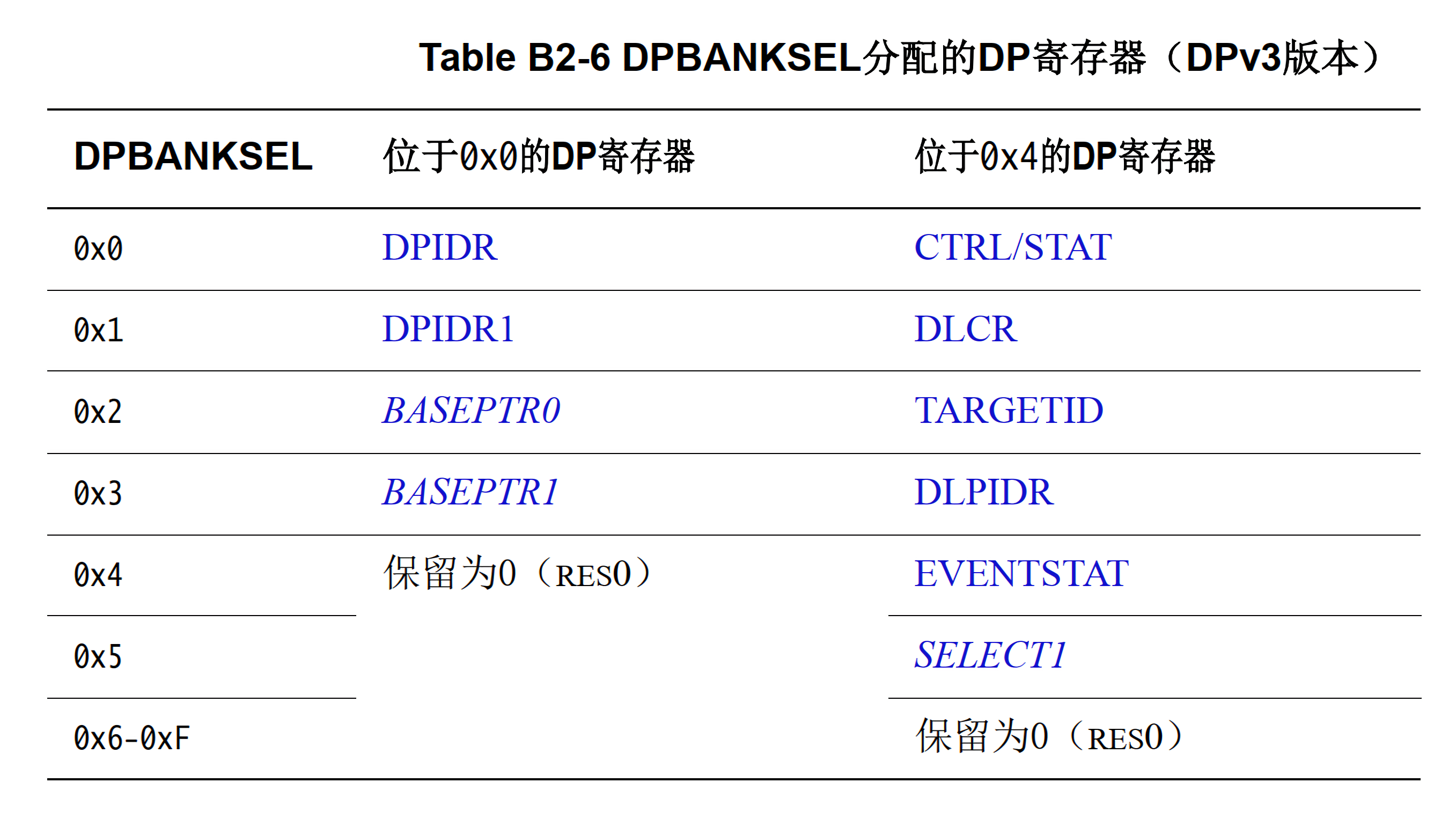

SELECT.DPBANKSEL字段决定了地址0x0和0x4将访问哪个寄存器。

表B2-3展示了DPv3的寄存器映射:

在DP中,使用ABORT寄存器请求中止事务的特性是可选的:

ABORT是否实现由实现决定(IMPLEMENTATION DEFINED)。如果

ABORT已经实现,那么如何访问它将由数据链路定义(DATA LINK DEFINED):- 如果其由数据链路所定义,那么DP寄存器0将被保留为此目的。

- 在JTAG-DP中,

ABORT寄存器将以ABORT指令的形式来实现。

- 如果在DP中实现了

ABORT寄存器,该寄存器是否能中止对AP的未完成事务的特性是可选的。如果一个正在进行的事务无法被中止,那么这保证了这个组件在系统复位之前无法进行访问。

ARM建议DP实现请求中止事务特性。

寄存器映射,对保留地址的访问

这些图中展示了对DP和AP的寄存器地址映射:

- 图A1-3(ADIv6实现的结构,演示了DPv3 JTAG-DP对通用AP的访问)。用于访问JTAG-DP寄存器。

- 图C2-1,用于访问MEM-AP寄存器。

- 图C3-1,用于访问JTAG-AP寄存器。

这些寄存器映射中存在一些保留地址。保留的AP寄存器地址保留为0(RES0)

DP寄存器的完整说明

在本章节中,将给出有关DP寄存器的完整说明。

下面的寄存器将以字母序逐个列出。

ABORT,中止操作寄存器

作用

ABORT用于强制中止一次AP事务。

从软件的角度看,中止是一个致命的操作。它将丢弃所有未进行和进行中的事务,并导致AP进入不可预测的状态(UNPREDICTABLE state)。不过,对于SW-DP,黏性(sticky)错误位不会被清除为0b0。

向ABORT.DAPABORT写0b1将会发起一次AP中止请求,这将导致当前的AP事务被取消。此外,当事务计数器可用时,此操作还会中止事务计数器。实现将定义(IMPLEMENTATION DEFINED)AP是否传播中止请求,例如通过中止一个正在进行中的事务来实现这一点。

当发生一次AP中断后:

- 由实现来决定(IMPLEMENTATION DEFINED)发生AP中断后哪些寄存器可以被访问。如果寄存器不可访问,DP将对AP访问请求发出

WAIT响应。ARM建议:任何与延迟(stalling)事务没有直接关联的AP寄存器都应允许访问,以便调试器诊断错误的原因。 - 允许通过DP访问和AP访问对其他的AP和组件进行访问。

警告:仅在极端条件下使用这一功能,例如调试器主机软件观察到目标硬件发生了长时间的停滞。如果目标硬件重复发出

WAIT响应,则表明其进入停滞状态。

使用限制、适用性、属性

使用限制

寄存器的访问类型为只写(RO)

适用性

包含在所有的实现中。

属性

一个32位的只写DP寄存器。

ABORT字段说明

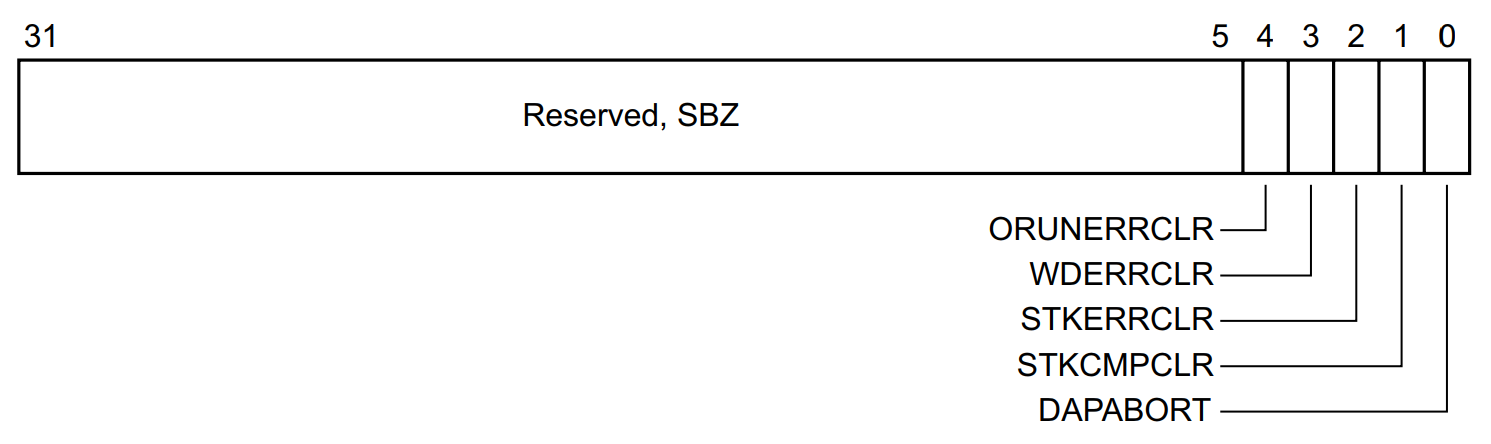

ABORT寄存器的位分配如下图所示:

- Bits[31:5]: 保留。应为0(Reserved,SBZ)

- ORUNERRCLR, bit[4]:向此位写

0b1将清除CTRL/STAT.STICKYORUN超时错误位。 - WDERRCLR, bit[3]: 向此位写

0b1将清除CTRL/STAT.WDATAERR写数据错误位。 - STKERRCLR, bit[2]: 向此位写

0b1将清除CTRL/STAT.STICKYERR迟滞错误位。 - STKCMPCLR, bit[1]: 向此位写

0b1将清除CTRL/STAT.STICKYCMP迟滞比较位。由实现来决定(IMPLEMENTATION DEFINED)迟滞比较位是否实现。见MINDP,最小化的DP扩展一节。 - DAPABORT, bit[0]: 向此位写

0b1将产生一次AP中断,用以中止当前的AP事务。注意,仅在调试器长时间收到WAIT响应时,才进行这个写入操作。

访问ABORT寄存器

如何对ABORT寄存器访问是由数据链路决定的(DATA LINK DEFINED):

- JTAG-DP: 通过其本身的扫描链进行访问。详见ABORT,JTAG-DP Abort寄存器一章。

- SW-DP: 在DP寄存器映射的偏移

0x0处进行写操作以访问。

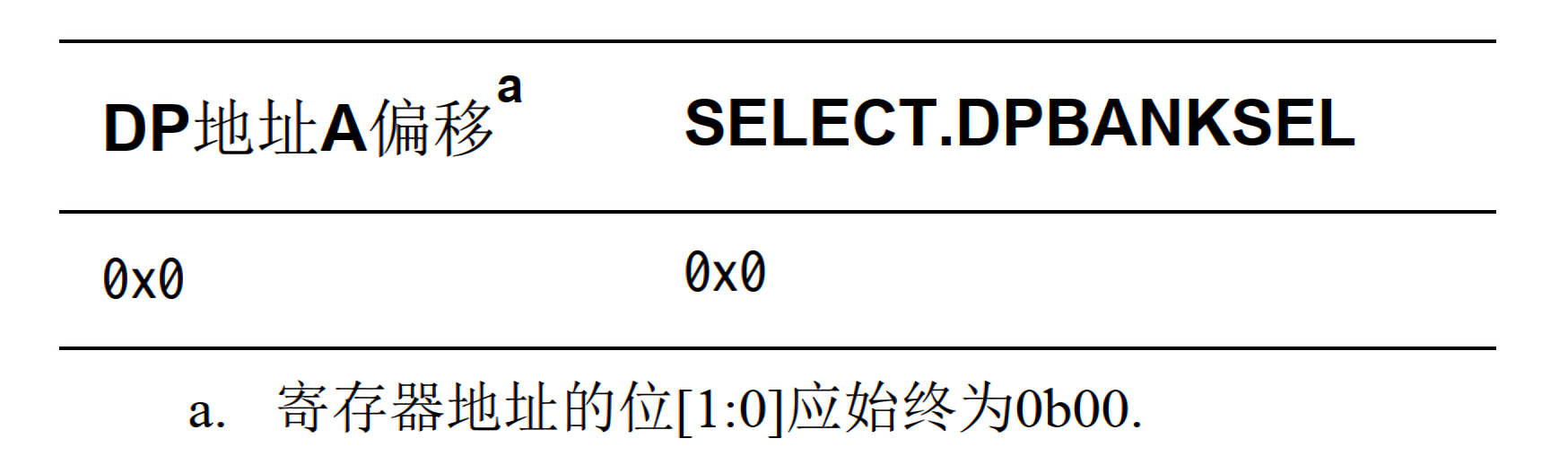

BASEPTR0-BASEPTR1, 基址寄存器0-1

作用

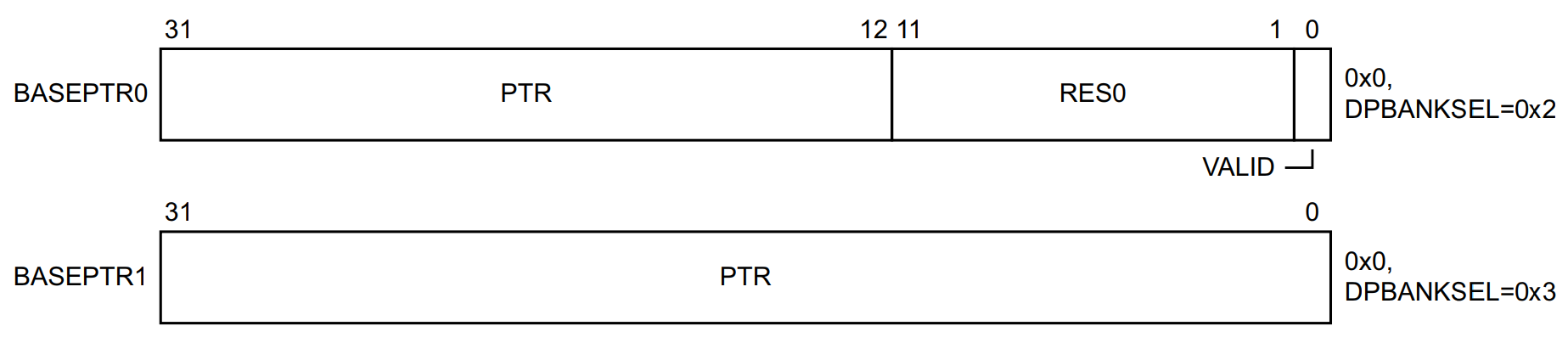

BASEPTR0和BASEPTR1为系统中的第一个组件提供了初始系统地址。一般情况下,系统地址是顶层ROM表地址,表明了APv2版本的AP位置。

地址的位宽由DPIDR1.ASIZE决定。DPIDR1.ASIZE表明了包含地址位[11:0]在内的完整地址位宽,而地址位[11:0]应当始终为0。举个例子,如果DPIDR1.ASIZE表示一个32位地址,BASEPTR0则用于表示基址的位[31:0],位[11:0]始终为0。未实现的位保留为0(RES0)。

作者注: 这里的地址要求4KB对齐,故位[11:0]为0。

使用限制、适用性、属性

使用限制

- 如果

DPIDR1.ASIZE表示一个12位地址,那么字段BASEPTR0.PTR和BASEPTR1.PTR保留为0(RES0)。 - 如果在地址

0x000处存在组件,那么BASEPTR0.VALID必须为0b1,否则必须为0b0。

该寄存器的默认访问形式为:只读(RO)。

适用性

包含在所有的实现中。

属性

BASEPTR0和BASEPTR1,两个32位的DP寄存器。

BASEPTR0-1字段描述

- PTR, BASEPTR1[31:0] : BASEPTR0[31:12]

系统第一个组件的基址,由BASEPTR1的位[31:0]和BASEPTR0的位[31:12]组成。其中,BASEPTR1.PTR对应基址位[63:32],BASEPTR0.PTR对应基址位[31:12]。

地址是4KB对齐的。

- BASEPTR0[11:0]

保留为0(Reserved, RES0.)

- VALID, BASEPTR0[0]

表明PTR字段是否指定了一个有效的基址。VALID位可能是以下的某个值:

0b0 未指定有效基址。PTR字段的值是未知的(UNKNOWN)。

0b1 PTR字段已指定一个有效基址。

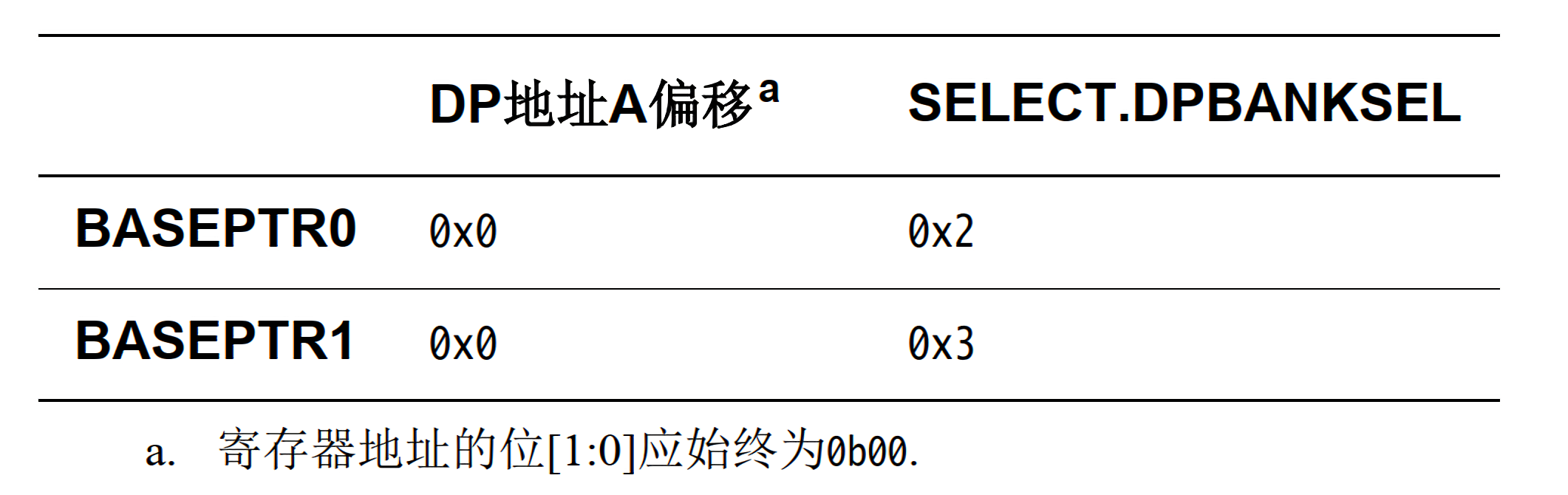

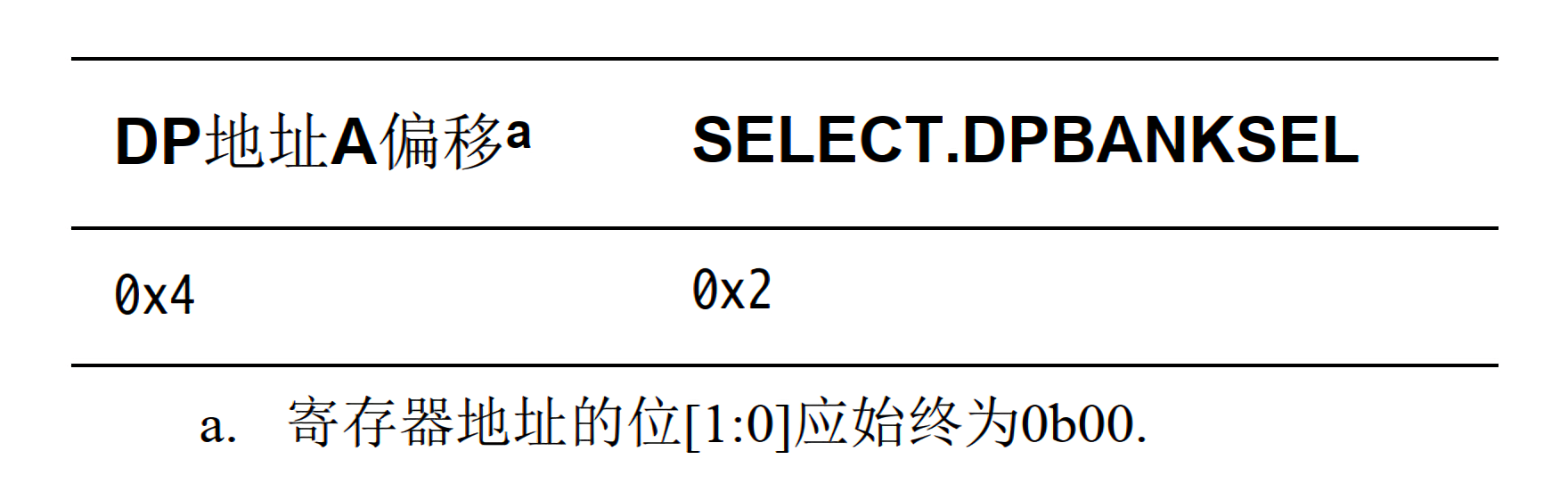

访问BASEPTR0与BASEPTR1寄存器

这两个寄存器可以通过下面的形式访问:

CTRL/STAT, 控制/状态寄存器

作用

DP架构中的控制/状态寄存器用于控制和获取关于DP的状态信息。

使用限制、适用性、属性

使用限制

下面的表将展示各个字段的访问方式,以及上电复位后的值。有一部分的字段是只读的(RO),其将忽略写操作。详见具体的字段描述。

适用性

包含在所有的实现中。

属性

CTRL/STAT是一个32位可读/可写寄存器。

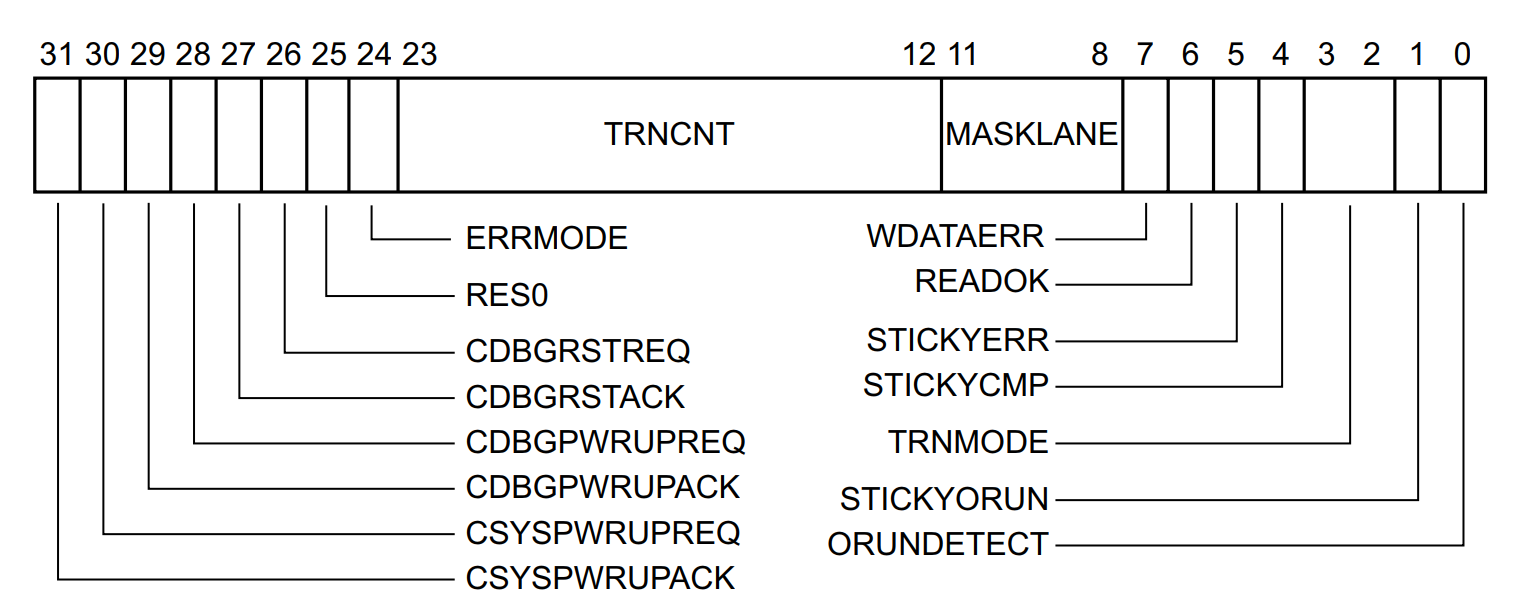

字段描述

- CSYSPWRUPACK, bit[31]

系统电源域上电确认(ACK)。指示CSYSPWRUPACK信号的状态。详见下文电源控制要求和操作一节。

该位为只读(RO),其将忽略写操作。

- CSYSPWRUPREQ, bit[30]

系统电源域上电请求。该位用于控制CSYSPWRUPREQ信号。详见下文电源控制要求和操作一节。

在上电复位后,该位的值为0b0。

- CDBGPWRUPACK, bit[29]

调试电源域上电确认(ACK)。指示了CDBGPWRUPACK信号的状态。详见下文电源控制要求和操作一节。

该位为只读(RO),其将忽略写操作。

- CDBGPWRUPREQ, bit[28]

调试电源域上电请求。该位用于控制CDBGPWRUPREQ信号。详见下文电源控制要求和操作一节。

在上电复位后,该位的值为0b0。

- CDBGRSTACK, bit[27]

调试复位确认(ACK)。指示了CDBGRSTACK信号的状态。详见下文调试复位控制行为一节。

该位为只读(RO),其将忽略写操作。

- CDBGRSTREQ, bit[26]

调试复位请求。该位用于控制CDBGRSTREQ信号。

由实现来决定(IMPLEMENTATION DEFINED)该位是可读可写(RW)还是读为0/写忽略(RAZ/W)

在上电复位后,此位的值为0b0。

更多的内容请见下文调试重置控制行为一节。

- Bit[25]

保留为0(Reserved, RES0)。

- ERRMODE, bit[24]

错误模式。指示了CTRL/STAT.STICKYERR字段的控制行为。详见之后关于STICKYERR字段的描述。

该字段在DPv3及其后续版本中引入。在早期的DP架构版本中,此位保留为0(RES0)。该字段可能会有以下的其中一个值:

0b0

AP事务中若出现错误,将设置CTRL/STAT.STICKYERR和CTRL/STAT.STICKYERR,直到他们被显式清除。

0b1

AP事务中若出现错误,将设置CTRL/STAT.STICKYERR,并且CTRL/STAT.STICKYERR将在FAULT响应做出后被清除。

当ERRMODE为0b1时,如果在AP事务中有错误产生,那么其可能会以FAULT响应的形式告知调试器,且不要求调试器主动地清除CTRL/STAT.STICKYERR。造成FAULT响应的JTAG-DP和SW-DP事务无法成功完成,在这种情况下CTRL/STAT.STICKYERR将被清除为0b0,以允许继续尝试之后的事务。

在上电复位后,此位的值为0b0。

- TRNCNT, bits[23:12]

事务计数器的计数值。见事务计数器一节。

在上电复位后,此位的值是未知的(UNKNOWN)。

注意: 该位由实现来决定(IMPLEMENTATION DEFINED)是否实现。在最小化的DP配置中,该位不受支持,且向

TRNCNT或TRNMODE写入非零值造成的结果是不可预测的(UNPREDICTABLE)。见MINDP,最小化的DP扩展一节。

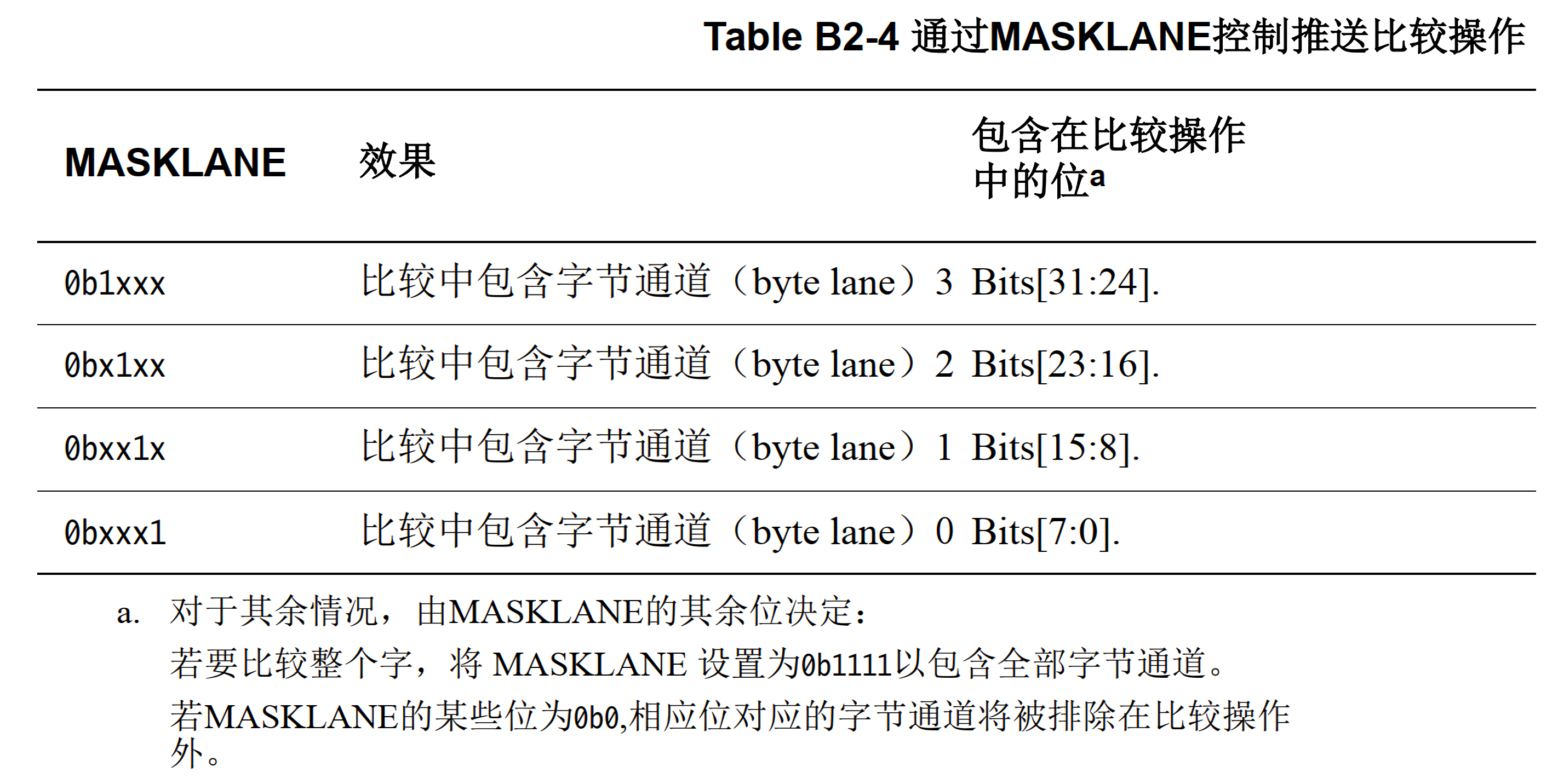

- MASKLANE, bits[11:8]

在推送(pushed)操作中,DP对AP写事务中提供的字与目标AP地址的当前字进行逐个字节的比较。MASKLANE用于设置哪些字节将被包含在比较操作中。更多信息,详见推送比较与推送验证操作一节。

MASKLANE字段长4位,每个位都对应一个4字节长的字比较操作。因此,每个位被称为控制比较操作的一个字节通道(byte lane)。

表B2-4展示了MASKLANE的位是如何控制比较的掩码(mask)操作的。

注意:

MASKLANE仅在传输模式寄存器TRNMODE设置为0b01(用于推送验证操作)或设置为0b10(用于推送比较操作)时才有意义。详见推送比较与推送验证操作一节。- 由实现来决定(IMPLEMENTATION DEFINED )是否要实现

MASKLANE。详见MINDP,最小化的DP扩展一节。 - 当上电复位后,

MASKLANE的值是未知的(UNKNOWN)。

- WDATAERR, bit[7]

当有写数据错误发生时,该位将被设置为0b1, 可能的情况有:

- 在写入操作的数据阶段发生奇偶校验或帧错误。

- 一次写操作已经被DP接受,但在推送到AP之前被取消。

更多信息,详见sticky标志与DP错误响应。

如何访问和清除该字段由数据链路来决定(DATA LINK DEFINED):

对于所有的JTAG-DP实现

访问保留为0(RES0)。

对于所有的SW-DP实现

- 访问方式为只读/写忽略(RO/WI)。

- 向

ABORT寄存器的WDERRCLR字段写0b1将会清除WDATAERR字段为0b0。如果有必要的话,一次单独对ABORT寄存器的写操作可以用于清除多个标志。

当清除WDATAERR标志后,通常情况下您必须重新发送之前出错的数据。

在上电复位后,WDATAERR的值为0b0。

- READOK, bit[6]

该位由数据链路定义(DATA LINK DEFINED):

- 对于JTAG-DP,该位保留为0(RES0)。

- 对于SW-DP,该位为只读/写忽略(RO/WI)。

若此前读AP或读RDBUFF的响应为OK,则该位将设置为0b1,若响应不是OK,该位被清除为0b0。

该位总是用于指示最后一次读AP的响应。详见协议错误响应一节。

在上电复位后,该位的值为0b0。

注意: 该字段仅在DPv1或更高版本中定义。

- STICKYERR, bit[5]

当一次AP事务返回错误时,该位将被设置为0b1。详见sticky标志与DP错误响应一节。

如何访问和清除该字段由数据链路来决定(DATA LINK DEFINED):

对于所有的JTAG-DP实现

- 访问形式是读/写1清除(R/W1C)。

- 向该位写

0b1将清除STICKYERR为0b0。如果有必要的话,对CTRL/STAT寄存器的一次写入可以用于清除多个标志。此外,向ABORT.STKERRCLR字段写入0b1也可以清除STICKYERR。

对于所有的SW-DP实现

- 访问形式是只读/写忽略(RO/WI)。

- 向

ABORT.STKERRCLR字段写入0b1以清除STICKYERR。如果有必要的话,单次对ABORT寄存器的写操作可以用于清除多个标志。

在清除CTRL/STAT.STICKYERR之后,您必须找出是哪里产生了使得该位被设置的错误。

在上电复位后,该位的值为0b0。

- STICKYCMP, bit[4]

在推送比较操作中发现不匹配的地方,或者在推送验证操作中发现结果匹配时,该位将被设置为0b1。详见推送比较与推送验证操作一节。

该位是否实现由实现来决定(IMPLEMENTATION DEFINED)。详见MINDP,最小化的DP扩展一节。

如何访问和清除该字段由数据链路来决定(DATA LINK DEFINED):

对于所有的JTAG-DP实现

- 访问形式是读/写1清除(R/W1C)。

- 向该位写

0b1将清除STICKYCMP为0b0。如果有必要的话,对CTRL/STAT寄存器的一次写入可以用于清除多个标志。此外,向ABORT.STKERRCLR字段写入0b1也可以清除STICKYERR。

对于所有的SW-DP实现

访问形式是只读/写忽略(RO/WI)。

向ABORT.STICKYCMP字段写入0b1以清除STICKYCMP。如果有必要的话,单次对ABORT寄存器的写操作可以用于清除多个标志。

在清除CTRL/STAT.STICKYCMP之后,您必须检查事务计数器的值,以找出是什么地方导致该位被设置。

在上电复位后,该位的值为0b0。

- TRNMODE, bits[3:2]

该位用于设置AP操作的传输模式。

对于常规的传输模式,AP事务将传递给AP进行处理。详见通过AP访问调试资源一节。

对于推送验证和推送比较操作,DP将比较目标AP地址保存的值和提供给AP写事务的值。AP写事务将产生一次对调试内存系统的访问。详见推送比较和推送验证操作一节。

TRNMODE可能是如下的一个值:

0b00 常规模式0b01 推送验证模式0b10 推送比较模式0b11 保留

在上电复位后,该字段的值是未知的(UNKNOWN)。

注意:由实现来决定(IMPLEMENTATION DEFINED)该字段是否被实现。在最小化的DP配置中,不支持

TRNMODE字段,此时向TRNCNT或TRNMODE写入非零值的结果是不可预测的(UNPREDICTABLE)。详见MINDP,最小化的DP扩展一节。

- STICKYORUN, bit[1]

若启用了超时(overrun)检测功能,该位将在发生超时的情况下被设置为0b1。见位[0]关于此寄存器启用超时检测功能的详细描述。

如何访问和清除该字段由数据链路来决定(DATA LINK DEFINED):

对于所有的JTAG-DP实现

访问形式是读/写1清除(R/W1C)。

向该位写0b1将清除STICKYORUN为0b0。如果有必要的话,对CTRL/STAT寄存器的一次写入可以用于清除多个标志。此外,向ABORT.STKERRCLR字段写入0b1也可以清除STICKYORUN。

对于所有的SW-DP实现

访问形式是只读/写忽略(RO/WI)。

向ABORT.ORUNERRCLR字段写入0b1以清除ORUNERRCLR。如果有必要的话,单次对ABORT寄存器的写操作可以用于清除多个标志。

在清除CTRL/STAT.STICKYORUN之后,您必须找出是哪个AP或DP事务导致了超时错误的发生,并根据事务计数器所指示的值重新进行相应的AP或DP事务。

在上电复位后,该位的值为0b0。

- ORUNDETECT, bit[0]

该位可能是以下的其中一个值:

0b0 禁用超时检测功能。

0b1 启用超时检测功能。

更多的信息,请见sticky标志与DP错误响应一节。

在上电复位后,该位的值为0b0。

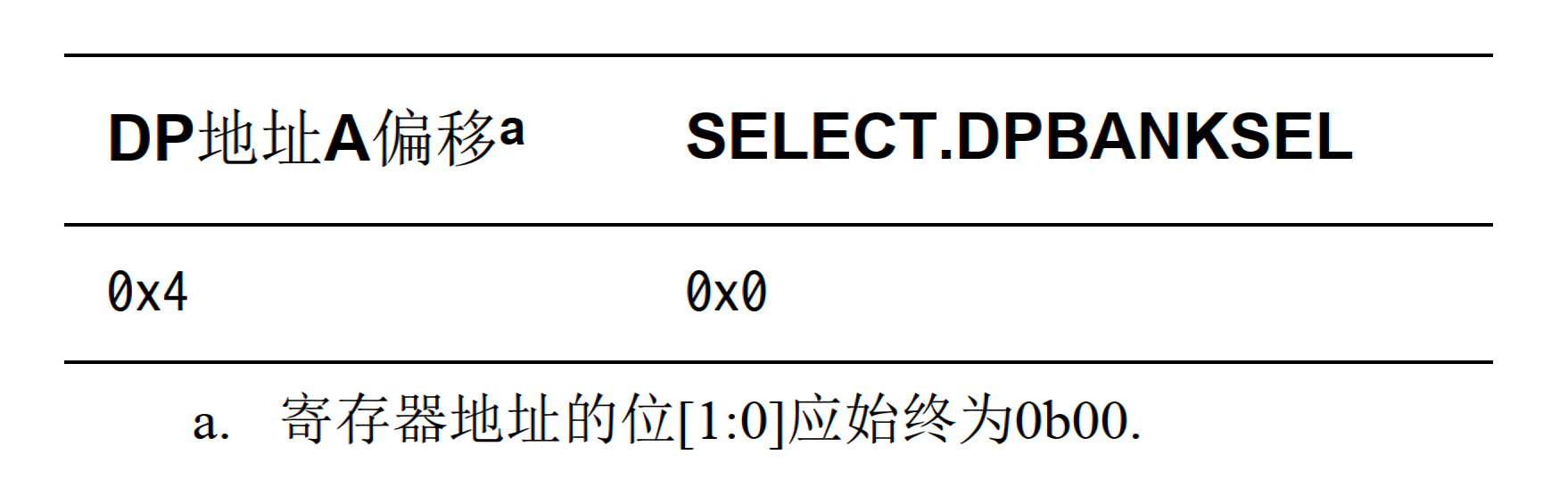

访问CTRL/STAT寄存器

可以通过如下地址访问CTRL/STAT寄存器:

DLCR, 数据链路控制寄存器

作用

用于控制数据链路的模式。

使用限制、适用性、属性

使用限制

该寄存器由数据链路定义(DATA LINK DEFINED):

- 对于JTAG-DP,该寄存器保留为0(RES0)。

- 对于SW-DP,在接下来的字段描述中将具体描述该寄存器。

该寄存器的访问方式为可读可写(RW)。

适用性

包含在所有的实现中。

属性

这是一个32位的由数据链路定义(DATA LINK DEFINED)的DP寄存器。

字段描述

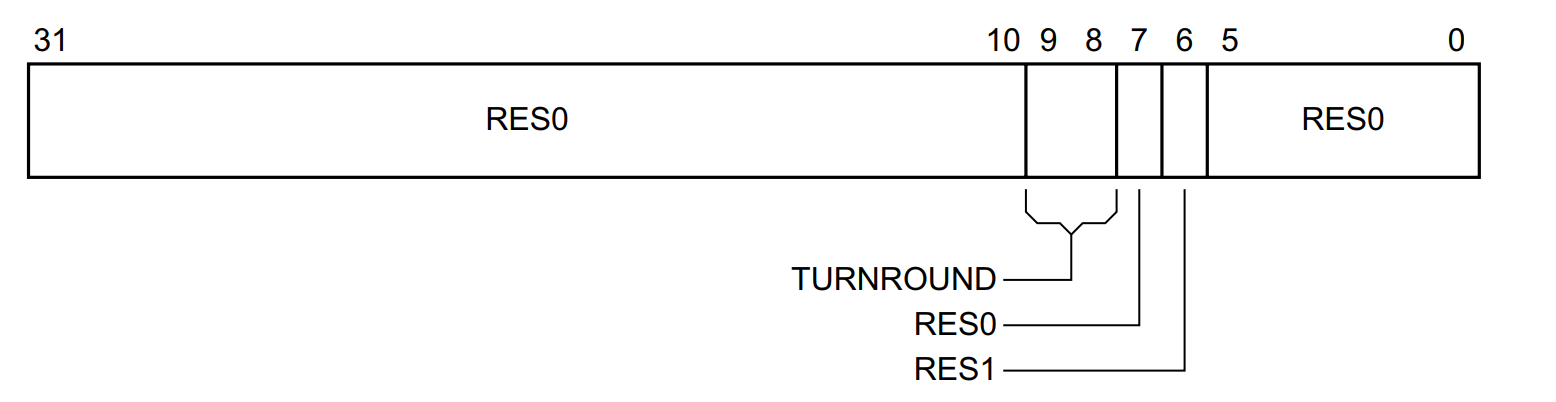

用于SW-DP的DLCR寄存器位分配如下:

- Bits[31:10]

保留为0(Reserved, RES0)。

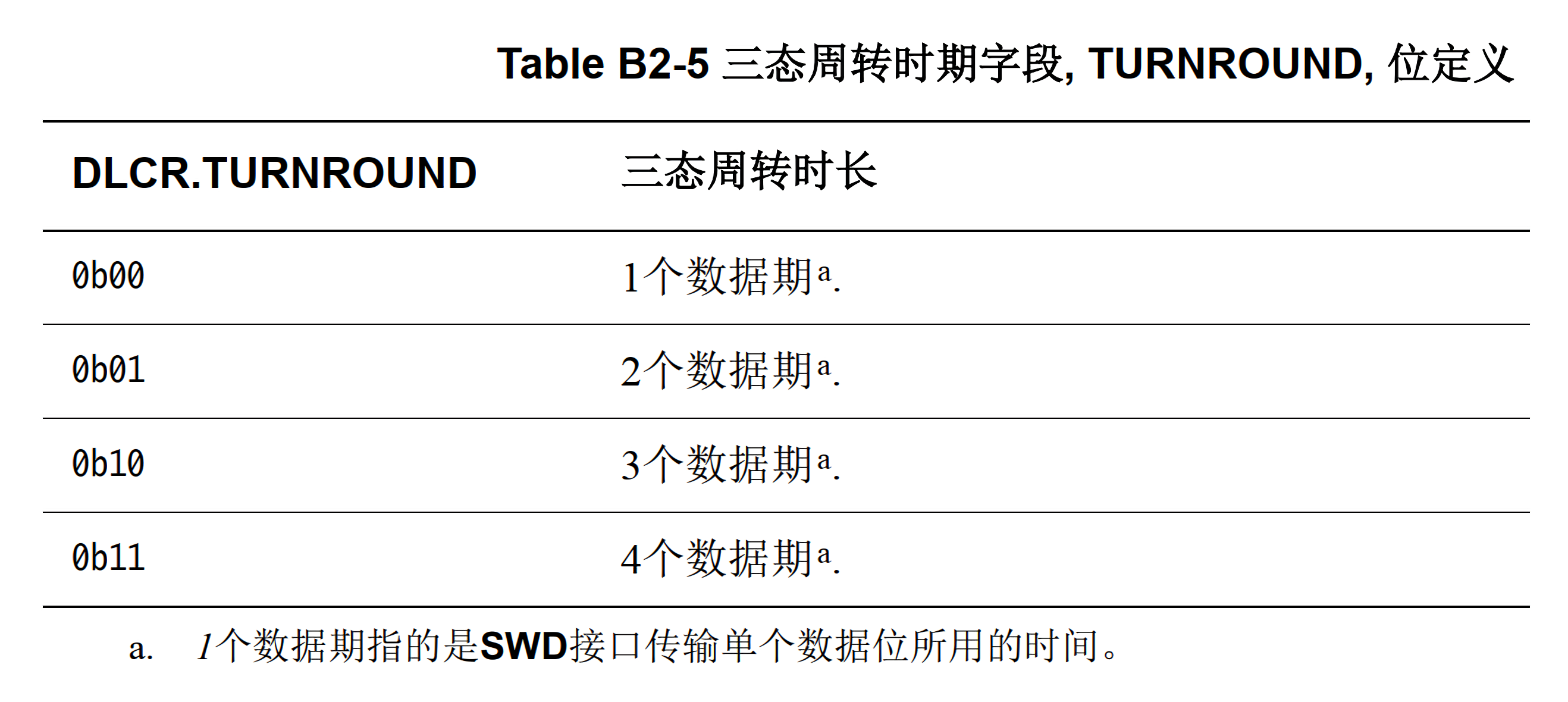

- TURNROUND, bits[9:8]

对于SW-DP,该位定义了三态周转(turnaround)的时间。详见线路周转一节。表B2-5展示了允许的值以及其对应的周转时长。

在上电复位后,该字段的值为0b00。

注意:是否支持可变周转期是由实现决定的(IMPLEMENTATION DEFINED)。如果实现不支持改变周转期,那么其必须对往

TURNROUND写入非零值的操作立即产生一次的协议错误。

- Bit[7]

保留为0(Reserved, RES0)。

- Bit[6]

保留为1(Reserved, RES1)。

- Bits[5:0]

保留为0(Reserved, RES0)。

访问DLCR寄存器

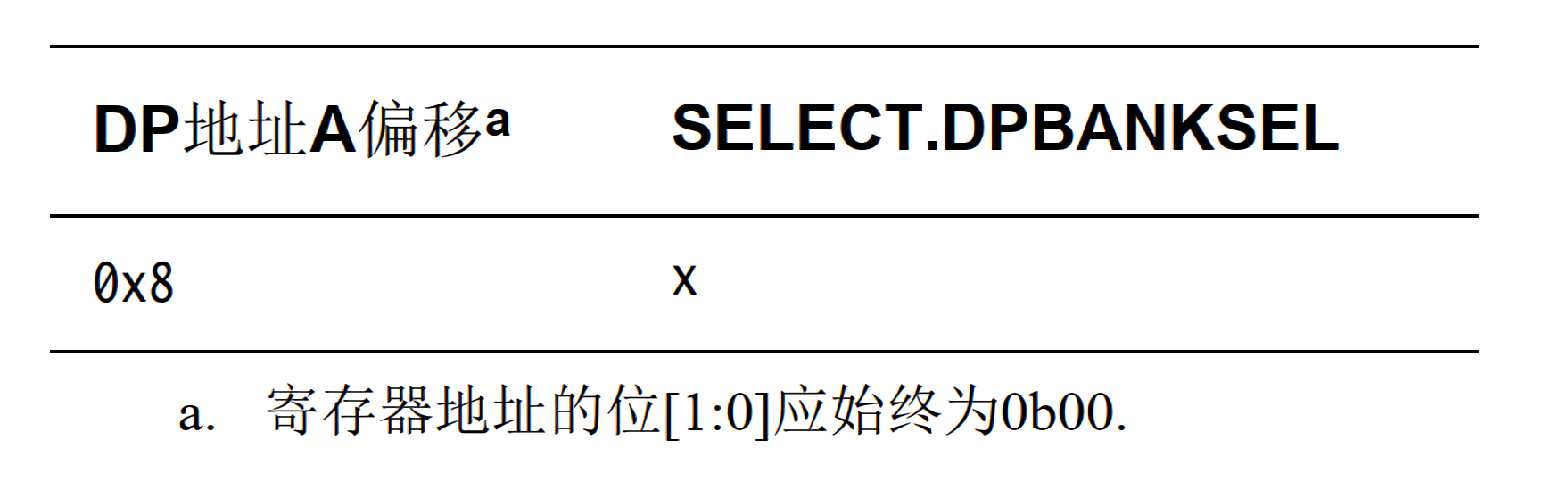

DLCR寄存器可以通过以下地址访问:

DLPIDR, 数据链路协议标识寄存器

作用

用于提供协议版本信息。

使用限制、适用性、属性

使用限制

该寄存器的访问方式是只读的(RO)。

适用性

包含在所有的实现中。

对于SW-DP配置:SWD端口实现的最低版本为SWD协议版本2。

对于JTAG-DP配置:JTAG端口实现的最低版本为JTAG协议版本1。

适用性

这是一个32位的由数据链路定义(DATA LINK DEFINED)的DP寄存器。

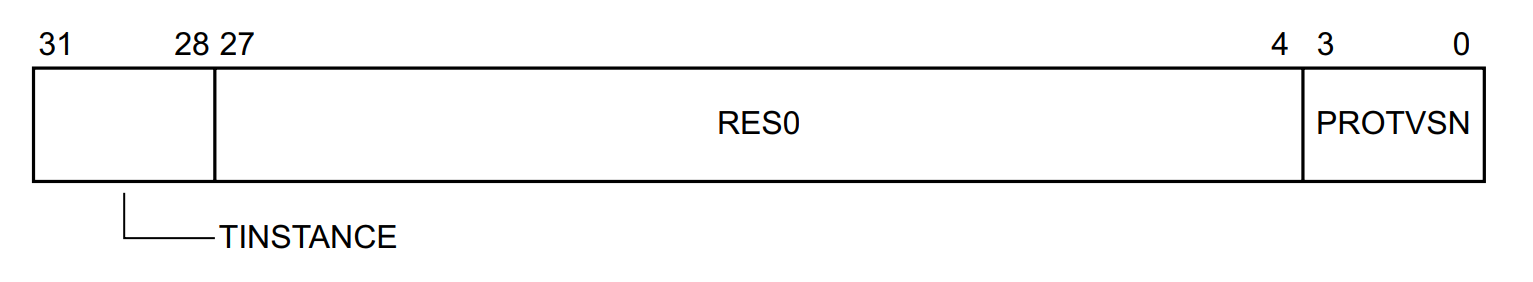

字段描述

- TINSTANCE, bits[31:28]

由实现定义(IMPLEMENTATION DEFINED)。定义了该设备的接口编码。这个编码值对于所有一同接入多点架构(multi-drop)系统且具有相同的TARGETID.TPARTNO与TARGETID.TDESIGNER字段值的全体设备必须是唯一的。

作者注:在多点架构系统中,唯一的编码值用于区分出接入的多个相同设备。

- Bits[27:4]

保留为0(RES0)。

- PROTVSN, bits[3:0]

定义实现了哪个SWD或JTAG协议版本。

对于SW-DP,可能是以下的一个值:

0x1 SWD协议版本2。添加了对多点架构的扩展支持。 见SWD一节。

其他值 保留。对于JTAG-DP,可能是以下的一个值:

0x0 JTAG-DP版本0。

0x1 JTAG-DP版本1。

其他值 保留。访问DLPIDR寄存器

DLPIDR寄存器可以通过以下地址访问:

DPIDR,调试端口标识寄存器

作用

用于提供调试端口的相关信息。

使用限制、适用性、属性

使用限制

该寄存器的访问方式是只读的(RO)。

适用性

包含在所有的实现中。

注意: 在DPv0中,

DPIDR是保留的,对其进行访问造成的结果是不可预测的(UNPREDICTABLE)。注意: 在所有的DP架构版本中,JTAG-DP均需要实现IDCOD指令和IDCODE扫描链。本架构并不要求TAP IDECODE寄存器的值与DPIDR的值保持一致。

属性

这是一个32位DP寄存器。

对DPIDR的访问不受SELECT.DPBANKSEL值的影响。

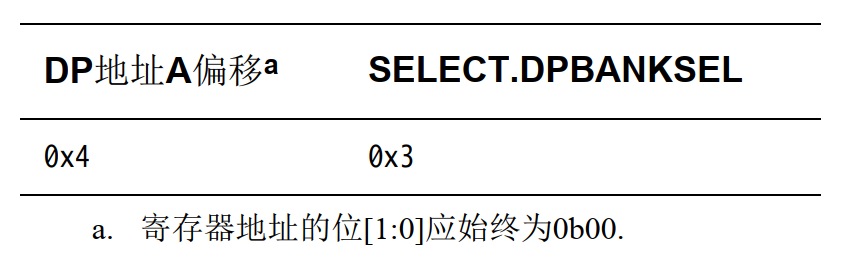

字段描述

- REVISION, bits[31:28]

修订代码号。该值由实现定义(IMPLEMENTATION DEFINED)。

- PARTNO, bits[27:20]

调试端口的制造商编码。该值由调试端口的设计者决定,且不可更改。

- Bits[19:17]

保留为0(RES0)。

- MIN, bit[16]

最小化DP(MINDP)功能的实现情况:

0b0 已实现事务计数器,推送验证和推送比较功能

0b1 未实现事务计数器,推送验证和推送比较功能。- VERSION, bits[15:12]

调试端口实现的架构版本。可能的值有:

0x0 保留。DPv0实际上未实现`DPIDR`寄存器。

0x1 实现的版本为DPv1。

0x2 实现的版本为DPv2。

0x3 实现的版本为DPv3。

其余值均为保留的。- DESIGNER, bits[11:1]

DP设计者的标识代码。该字段用于标识DP的设计者(不是实现者,除非二者相同)。关于如何获得标识代码,或者如何将这些代码进行赋值,请联系JEDEC: http://www.jedec.org

一个JEDEC代码采用以下形式:

- 由零个或多个

0x7F组成的数字序列 - 之后跟着一个8位的数字,该数字不能是

0x7F且该数字的位[7]为其奇校验位。例如,ARM公司分配的代码为0x7F 0x7F 0x7F 0x7F 0x3B。

用于DPIDR的编码具有以下形式:

DPIDR bits[11:8],代表JEP106延续代码(continuation code)。DPIDR bits[11:8]表示了在最终数字之前,0x7F的出现次数。例如,对于ARM公司,该位域的值为0x4。DPIDR bits[7:1],代表JEP106标识代码(identification code)。其等价于JEDEC代码的最终代码中的位[6:0]。例如,对于ARM公司,该位为0x3B。

- Bit[0]

读为0(RAO)。

访问DPIDR寄存器

DPIDR寄存器可以通过以下地址访问:

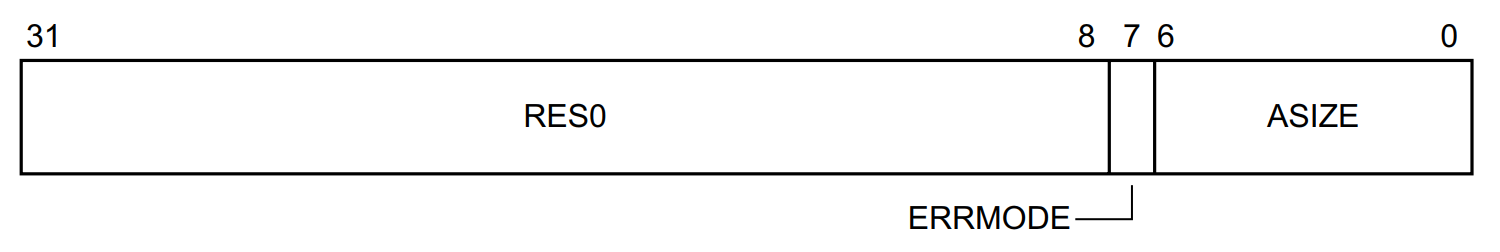

DPIDR1, 调试端口标识寄存器1

作用

用于提供调试端口的相关信息。

使用限制、适用性、属性

使用限制

对DPIDR1的读取操作必须立即被处理,且不能发出WAIT响应。

该寄存器的访问方式是只读的(RO)。

适用性

包含在所有的实现中。

属性

这是一个32位DP寄存器。

对DPIDR1的访问不受SELECT.DPBANKSEL值的影响。

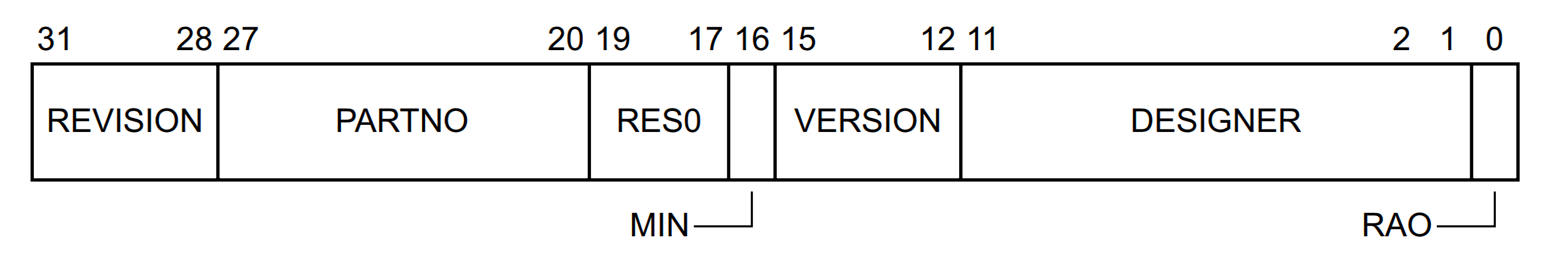

字段描述

- Bits[31:8]

保留为0(RES0)

- ERRMODE, bit[7]

是否支持错误汇报模式。该字段可能的值为:

0b0 未实现`CTRL/STAT.ERRMODE`。

0b1 已实现`CTRL/STAT.ERRMODE`。- ASIZE, bits[6:0]

地址宽度。该字段指定了SELECT、SELECT1、BASEPTR0和BASEPTR1寄存器所使用的地址宽度大小,可能的值有:

0x0C 12位地址。

0x14 20位地址。

0x20 32位地址。

0x28 40位地址。

0x30 48位地址。

0x34 52位地址。

其余的值均为保留的。访问DPIDR1寄存器

DPIDR1寄存器可以通过以下地址访问:

EVENTSTAT, 事件状态寄存器

作用

系统通过EVENTSTAT寄存器向外部调试器发送事件信号。事件的类型是由实现定义(IMPLEMENTATION DEFINED)的。

ARM推荐将EVENTSTAT用于以下的情形:

- 带有软件确认(ACK)的CoreSight交叉触发接口(Cross-Trigger Interface, CTI)的触发输出。

单处理器系统的输出,用于指示处理器是否暂停(halted):

- 对于Armv6-M、Armv7-M和Armv8-M处理器,推荐使用

HALTED信号。 - 对于其他ARM架构处理器,推荐使用

DBGACK信号。

- 对于Armv6-M、Armv7-M和Armv8-M处理器,推荐使用

使用限制、适用性、属性

使用限制

该寄存器的访问方式是只读的(RO)。

适用性

包含在所有的实现中。

属性

这是一个32位的只读(RO)寄存器。

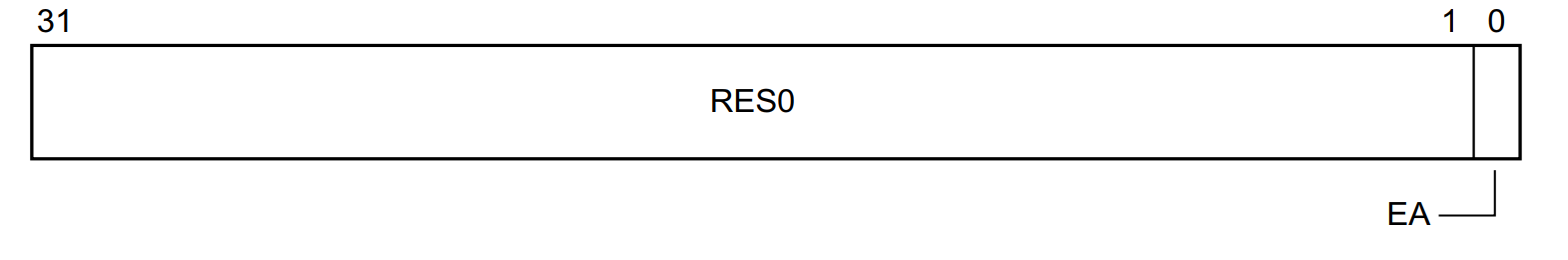

字段描述

- Bits[31:1]

保留为0(RES0)。

- EA, bit[0]

如果实现了事件,那么该位用于指示事件的状态。该位可能的值为:

0b0 有事件需要响应。

0b1 还没有事件需要响应。如果未实现事件,那么该字段是读为零(RAZ)的。

注意: 如上所示,事件的状态在寄存器中被颠倒了。当调试器在一个未实现事件的系统上进行调试时,调试器将把其读出的0值视作有事件需要进行响应,并检查其他的寄存器以确定系统的状态。

访问EVENTSTAT寄存器

EVENTSTAT寄存器可以通过以下地址访问:

RDBUFF, 读缓冲区寄存器

作用

RDBUFF的作用和表现方式由数据链路决定(DATA LINK DEFINED):

对于JTAG-DP

读缓冲区是由架构定义的,用于提供无副作用的DP读操作。该定义允许调试器在操作序列的末尾处插入一次对RDBUFF的DP读操作,以返回最终的AP读结果和ACK值。

对于SW-DP

在SW-DP上,读缓冲区用于表示在之前的AP读操作所捕获的数据,因此系统可以重复返回之前的值,而无需发起一次新的AP访问。

注意: 当读完DP读缓冲区后,缓冲区里面的内容不再有效。第二次对DP读缓冲区进行的读操作所获得的值是未知的(UNKNOWN)。

如果您想获得AP寄存器读操作的值,您可能需要采取以下任意一种方式:

- 再次进行AP寄存器访问,并确保当前已经正确选择AP寄存器。

- 对DP读缓冲区寄存器进行读取。

对于AP或DP的第二次访问将会停滞,直到首次AP读取的结果可用为止。

使用限制、适用性、属性

使用限制

该寄存器的访问方式是只读的(RO)。

适用性

包含在所有的实现中。

属性

这是一个32位的只读寄存器。

字段描述

- Bits[31:0]

由数据链路定义(DATA LINK DEFINED):

JTAG-DP: 读为0/写忽略(RAZ/WI)

SW-DP: 之前AP读操作的结果数据

访问RDBUFF寄存器

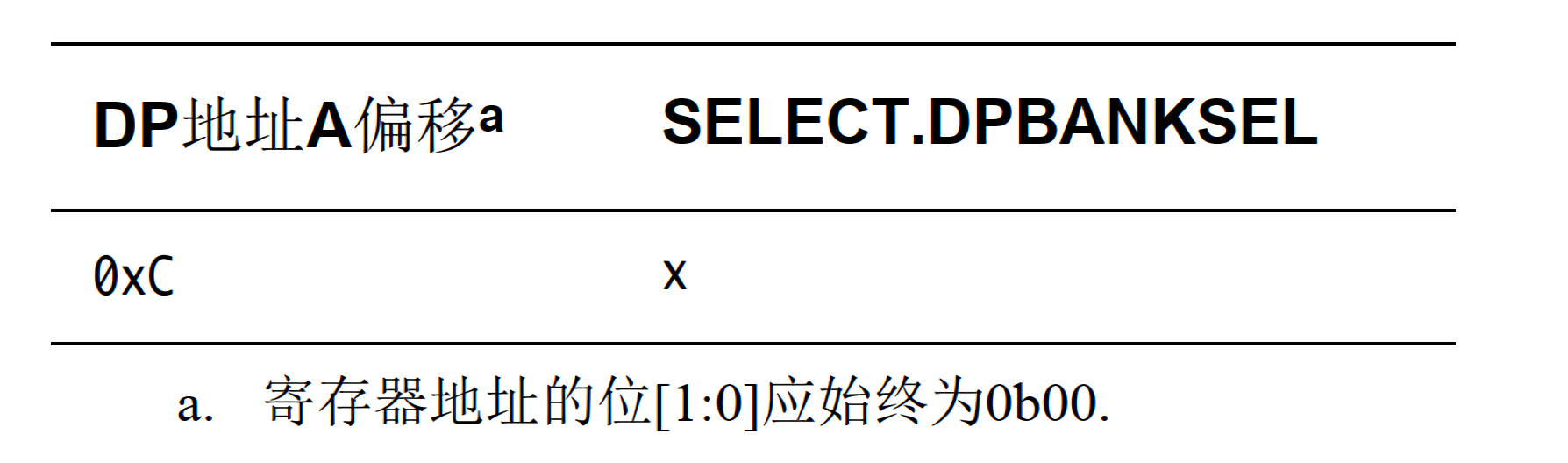

RDBUFF寄存器可以通过以下地址访问:

RESEND, 重发读结果寄存器

作用

对RESEND寄存器进行读操作并不会捕获来自AP的新数据,其将会返回最后一次AP读事务的结果,或者返回最后一次对DP寄存器RDBUFF读事务的结果。

RESEND寄存器使得调试器能够从出错的SW-DP传输事务中恢复读取数据,而不必重新发出原始的读取请求,且无需产生对于已连接的调试内存系统的新一轮访问。

RESEND寄存器能被多次访问。其将始终返回相同的值,直到有新的AP访问或者对DP寄存器RDBUFF的访问产生。

使用限制、适用性、属性

使用限制

ARM建议调试器当且仅当在SW-DP读事务失败后访问RESEND寄存器。这样做的原因是,如果实现不能重传信息,允许其将RESEND读操作事务视为一个协议错误(protocol error)。

该寄存器的访问方式是只读的(RO)。

适用性

包含在所有的实现中。

属性

这是一个32位的只读寄存器。

RESEND寄存器:

- 是一个只读(read-only)寄存器。

- 在DP寄存器映射中,以偏移

0x8的形式进行读取 由数据链路定义(DATA LINK DEFINED):

- JTAG-DP 该寄存器是保留的,任何的访问操作造成的结果将是不可预测的(UNPREDICTABLE)。

- SW-DP 该值返回上一次AP读事务的结果,或者对

RDBUFF的读结果。

字段描述

- Bits[31:0]

由数据链路定义(DATA LINK DEFINED):

JTAG-DP 该寄存器是保留的,任何的访问操作造成的结果将是不可预测的(UNPREDICTABLE)。

SW-DP 上一次AP读事务的结果。

访问RESEND寄存器

RESEND寄存器可以通过以下地址访问:

SELECT-SELECT1, AP选中寄存器组

作用

- 选中一个访问端口(AP)和该访问端口中的活动寄存器组(register bank)。

- 选中DP地址组(address bank)。

使用限制、适用性、属性

使用限制

该寄存器的访问方式是只写的(WO)。

适用性

包含在所有的实现中。

属性

两个32位的只写(WO)寄存器。

字段描述

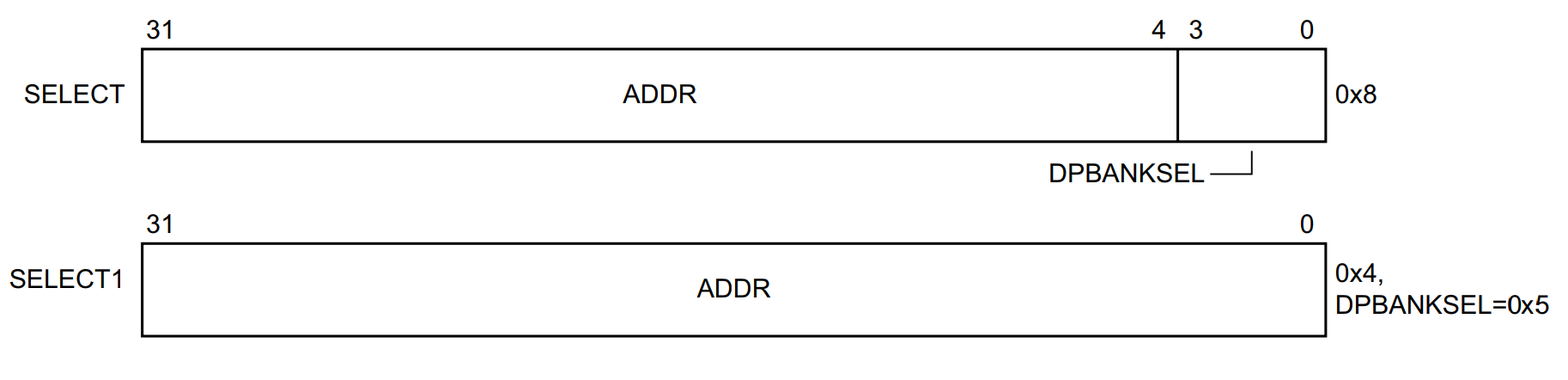

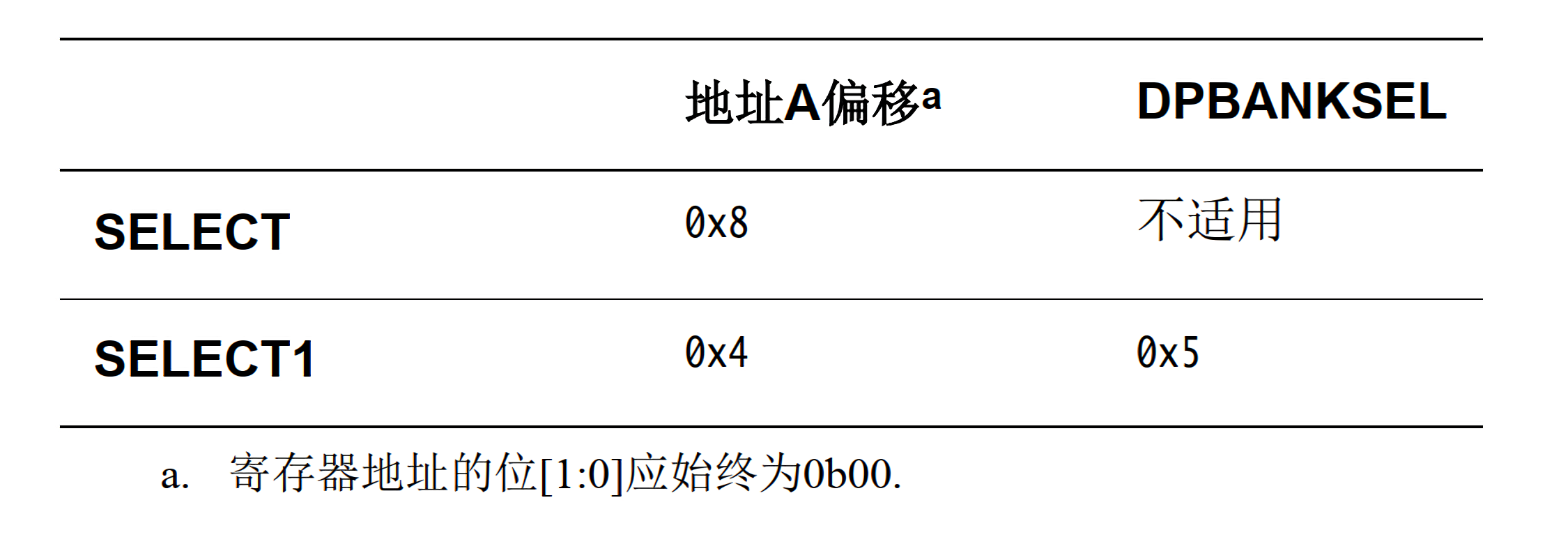

- ADDR, SELECT1 bits[31:0] : SELECT bits[31:4]

地址输出位[63:4],由SELECT1的位[31:0]和SELECT的位[31:4]连接而成。ADDR字段选中系统位置的一个4字组(4-word bank)进行访问。地址位[3:2]选中组(bank)中的一个特定寄存器,以供APACC事务进行。位[1:0]始终为0b00。

在上电重置或者SWD线路重置后,该字段的值是未知的(UNKNOWN)。

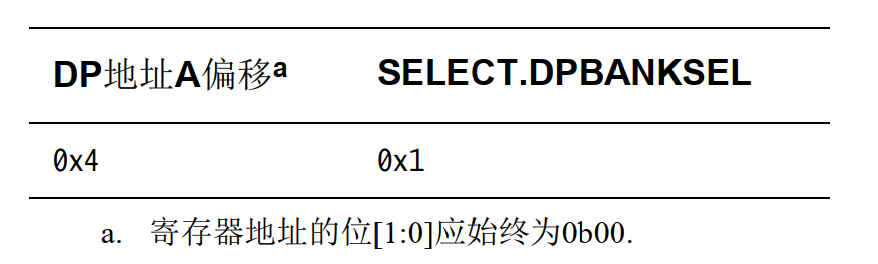

- DPBANKSEL, bit[3:0]

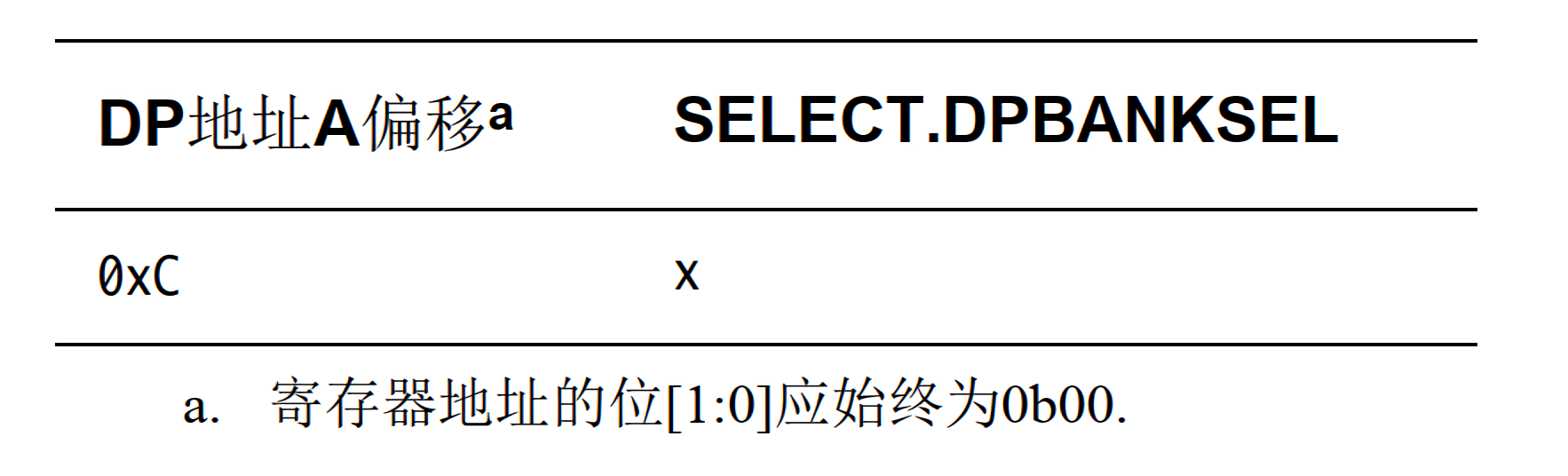

选中的调试端口地址组(address bank)。

SELECT.DPBANKSEL的行为表现取决于DP版本。在DPv3版本中,SELECT.DPBANKSEL字段控制地址0x0和0x4上的哪个DP寄存器被选中。表B2-6展示了该字段允许的值:

其余的SELECT.DPBANKSEL值为保留的。如果该字段设置为一个保留值,那么对于地址0x0和0x4的DP寄存器的访问操作将是RES0。

在上电复位后,该字段的值为0x0。

在SWD总线重置后,该字段必须重置为0x0

注意: 一些早期的ADI修订版本将

DPBANKSEL描述为一个仅包含单个位的字段CTRSEL,该字段仅在SW-DP中定义。

访问SELECT-SELECT1寄存器

SELECT-SELECT1寄存器可以通过以下地址访问:

TARGETID, 目标设备标识寄存器

作用

在主机连接了单个设备时,TARGETID寄存器用于提供目标设备的信息。

使用限制、适用性、属性

使用限制

该寄存器的访问方式是只读的(RO)。

适用性

包含在所有的实现中。

属性

一个32位的只读(read-only)寄存器。

字段描述

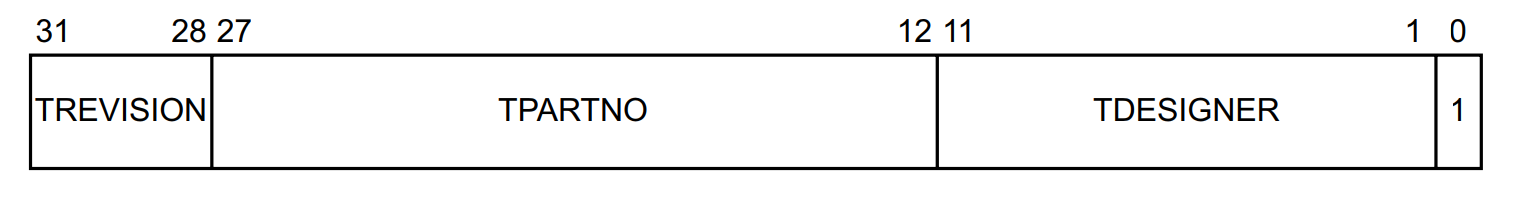

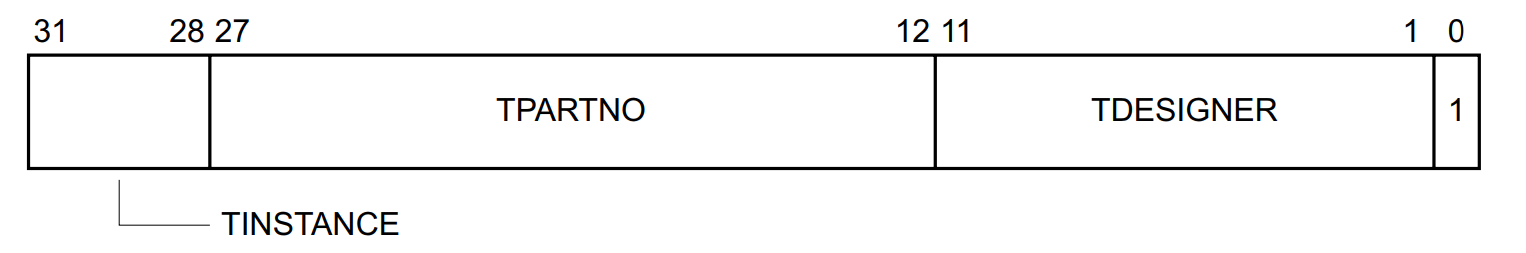

- TREVISION, bits[31:28]

目标设备的修订版本。

- TPARTNO, bits[27:12]

由实现定义(IMPLEMENTATION DEFINED)。这个值由该组件的设计者分配。对该组件而言必须是唯一的。

- TDESIGNER, bits[11:1]

由实现定义(IMPLEMENTATION DEFINED)。

该字段用于标识DP的设计者(不是实现者,除非二者相同)。

设计者必须在此插入JEDEC的分配代码。

注意: ARM的JEP106代码并未在

TDESIGNER中体现。ARM可能会设计包含TARGETID寄存器的DP,但在通常情况下,组件的设计者不是ARM,他们使用ARM授权的IP创建组件。 用于标识组件设计者的字段为TPARTNO。如果该组件是ARM设计的,那么该字段的值为0x23B。

关于如何获得标识代码,或者如何将这些代码进行赋值,请联系JEDEC: http://www.jedec.org

一个JEDEC代码采用以下形式:

- 由零个或多个

0x7F组成的数字序列。 - 之后跟着一个8位的数字,该数字不能是

0x7F且该数字的位[7]为其奇校验位。例如,ARM公司分配的代码为0x7F 0x7F 0x7F 0x7F 0x3B。

用于TARGETID的编码具有以下形式:

TARGETID bits[11:8],代表JEP106延续代码(continuation code)。TARGETID bits[11:8]表示了在最终数字之前,0x7F的出现次数。TARGETID bits[7:1],代表JEP106标识代码(identification code)。其等价于JEDEC代码的最终代码位[6:0]。

例如,对于ARM公司来说,延续值为0x4,代表着0x7F的出现次数,而ARM JEP106代码为0x3B,故最终的结果值为0x23B

作者注:此处的ARM延续代码为

b0100,0x4,标识代码为b0111011,0x3B。不过由于TDESIGNER分配到位[11:1],因此将二者组合并移位到[10:0]后的结果即为0x23B。

- Bit[0]

读为1(RAO)。

访问TARGETID寄存器

TARGETID寄存器可以通过以下地址访问:

TARGETSEL, 目标选择寄存器

作用

TARGETSEL寄存器用于在SWD多点架构(multi-drop)系统中选中一个目标设备。

在总线重置序列之后立即进行对TARGETSEL的写操作,如果满足以下的所有条件,将选中一个合适的目标设备:

- 位[31:28]与

DLPIDR的位[31:28]一致。 - 位[27:0]与

TARGETID的位[27:0]一致。

写入其他的值将取消选中设备。调试工具需要写入0xFFFFFFFF以取消选中所有的设备。0xFFFFFFFF是一个无效的TARGETID值。其余无效的TARGETID是保留的。

对TARGETSEL寄存器进行写操作的响应阶段,目标设备不会驱动总线。详见sticky标志与DP错误响应一节。

使用限制、适用性、属性

使用限制

该寄存器是数据链路定义的(DATA LINK DEFINED)。

JTAG-DP 该寄存器是保留的,所有对其的访问操作造成的结果将是不可预测的(UNPREDICTABLE)。

SW-DP 如果实现了SWD协议版本2,那么该寄存器是已经实现的。

该寄存器的访问方式是只写的(WO)。

适用性

包含在所有的实现中。

属性

一个32位的DP寄存器。

字段描述

对于SW-DP,TARGETSEL的字段分配如下:

- TINSTANCE, bits[31:28]

由实现定义(IMPLEMENTATION DEFINED)。是该设备的实例编号(instance number)。见DLPIDR寄存器。

- TPARTNO, bits[27:12]

由实现定义(IMPLEMENTATION DEFINED)。这个值由该组件的设计者分配。见TARGETID寄存器。

- TDESIGNER, bits[11:1]

由实现定义(IMPLEMENTATION DEFINED)。这个11位代码表示了JEDEC JEP106延续代码(continuation code)和标识代码(identity code)。见TARGETID寄存器。

- Bit[0]

应为1(SBO)。

访问TARGETSEL寄存器

TARGETSEL寄存器可以通过以下地址访问:

系统和调试电源控制行为

在这一章节中将详细讲述系统和调试电源的有关信息。

ADI电源域模型

ADI支持多种电源域,用于支持可以断电的调试组件。

- 始终开启的(always-on)电源域: 当调试器连接到设备时必须上电的电源域。

- 系统电源域: 包含系统组件的电源域。

- 调试电源域: 包含整个调试子系统的电源域 。

如果有必要的话,系统和调试电源域可以被细分。不过,为了定义一个简单的调试接口,设备必须在顶层被分为系统和调试电源域。任何更精细的控制操作超出了本模型的讨论范围。

在大多数情况下,调试器为整个SoC供电。然而,如果一个调试器正在检查电源管理问题,它有可能只想给调试域(domain)供电。为了实现这一点,SoC的设计者可能希望将电源控制器映射到一个总线的段(bus segment)上,在只有调试电源域通电的情况下,ADI可以访问这个总线的段。

在使用ADI的过程中,为了使调试正常进行,系统不能断开DP上的电源。如果DP的电源被断开,那么DP控制器的状态就会丢失。不过,ADI的设计使得您可以在保持DP供电的情况下,对ADI的其他部分进行断电并继续进行调试。

DP寄存器位于DP的外部接口侧,其对应的电源域为始终开启的(always-on)电源域。因此,它们总是可以被驱动,进而向系统电源控制器提出上电请求。电源和重置控制位是DP寄存器CTRL/STAT的一部分,关于此部分的更多内容,请参见下文中的调试复位控制行为。

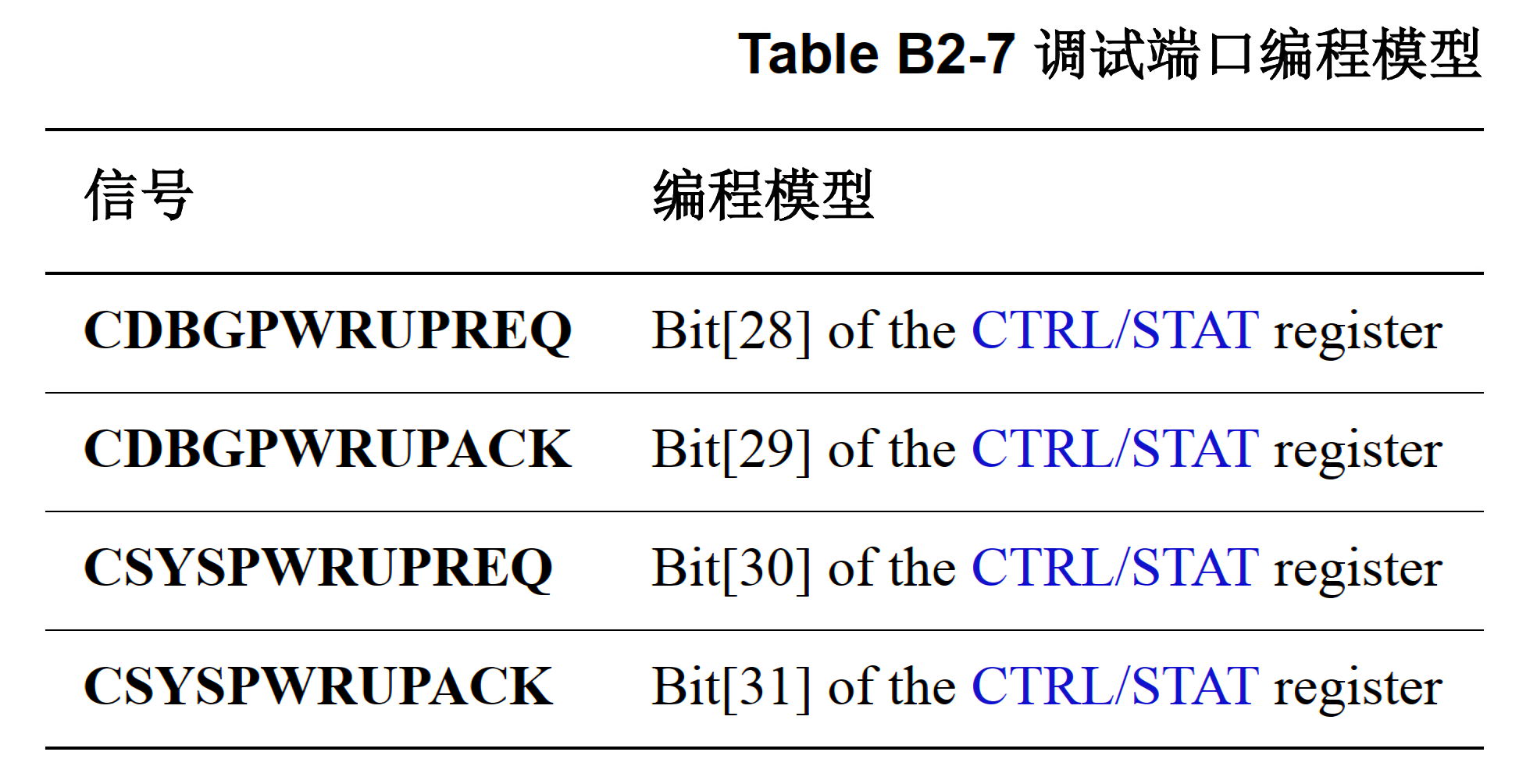

ADIv6 定义了两对电源控制信号:

CDBGPWRUPREQ和CDBGPWRUPACKCSYSPWRUPREQ和CSYSPWRUPACK

表B2-7总结了电源控制信号对的编程模型。

这些信号将用于向系统电源和时钟控制器提供请求。下面的章节描述了这些信号对。

CDBGPWRUPREQ和CDBGPWRUPACK

CDBGPWRUPREQ是从调试接口到电源控制器的信号。该信号要求系统电源控制器完全上电,并确保调试电源域中的时钟可用。

CDBGPWRUPACK是从电源控制器到调试接口的信号。当CDBGPWRUPREQ信号有效时,电源控制器对调试电源域上电,然后使得CDBGPWRUPACK信号有效,作为请求的响应。

CDBGPWRUPREQ控制调试电源域中的哪些组件是由实现决定的(IMPLEMENTATION DEFINED)。调试电源域或许包含系统中的所有调试组件,也可能排除某些组件,例如具有额外级别电源控制的组件。CDBGPWRUPREQ信号表明,调试器要求这些组件的调试资源是可通信的(communicative)。而可通信意味着调试器至少能够访问足够多包含调试资源的寄存器,以确定资源对应的状态。要包含哪些调试资源是由实现定义的(IMPLEMENTATION DEFINED)。电源和时钟控制器必须为尽可能多有需要的域进行上电并运行时钟,以满足调试器对资源进行通信的要求。

一旦CDBGPWRUPREQ信号有效,那么电源和时钟控制器就必须遵守该信号。例如,如果调试电源域中的一个组件要求关闭电源,该请求必须被该电源域中的非调试逻辑所模拟,包括所有具有单个共享域的组件。

如果一个组件的某些调试资源不在调试电源域内,那么至少其最小调试接口应当通电。如果满足以下要求,可以从组件的其余部分移除电源:

- 有办法可以保存和恢复调试资源的状态

- 当组件的其余部分没有供电时,调试器可以与调试资源通信。

在保存和恢复调试资源状态的各种办法中,包括由软件实现的解决方案。如果调试资源在组件的其余部分断电后丢失了它们所保存的值,那么调试接口必须实现用于告知调试器哪些值已经丢失的方法。

CDBGPWRUPACK信号是CDBGPWRUPREQ请求信号的响应。一旦CDBGPWRUPREQ信号被置为有效,CDBGPWRUPACK信号必须被置为有效。见下文上电请求与响应时序一节。

CSYSPWRUPREQ和CSYSPWRUPACK

CSYSPWRUPREQ是从调试端口到电源控制器的信号。该信号用于请求系统电源控制器完全上电,并确保系统电源域中的时钟可用。CSYSPWRUPACK是从电源控制器到调试接口的信号。当CSYSPWRUPREQ信号置为有效时,电源控制器将调试电源域上电,然后将CSYSPWRUPACK信号置为有效作为请求的响应。

CSYSPWRUPREQ控制系统电源域中的哪些组件是由实现决定的(IMPLEMENTATION DEFINED)。系统电源域或许包含系统中的所有调试组件,也可能排除某些组件,例如具有额外级别电源控制的组件,比如用于实现独立核心供电请求的处理器。

CSYSPWRUPREQ信号表明,调试器要求这些组件的所有调试组件都是生效的(active)。生效意味着调试资源可以执行其调试功能。一个生效的资源也是可以通信的(communicative)。

一旦CSYSPWRUPREQ信号有效,那么电源和时钟控制器就必须遵守该信号。

CSYSPWRUPREQ信号对那些受CDBGPWRUPREQ控制的调试组件没有影响,因为这些组件在系统电源域中没有调试逻辑。但是,对于由CSYSPWRUPREQ控制的系统电源域中某些调试资源的组件,必须对该电源域内的非调试逻辑进行模拟。

CSYSPWRUPACK信号是CSYSPWRUPREQ请求信号的响应。一旦CSYSPWRUPREQ信号有效,CSYSPWRUPACK信号必须被置为有效。见下文上电请求与响应时序一节。

一旦调试器发出了CSYSPWRUPREQ信号,也必须发出CDBGPWRUPREQ信号。

电源控制要求和操作

本节适用于系统和调试域,将使用以下符号:

CxxxPWRUPREQ,对应CSYSPWRUPREQ或CDBGPWRUPREQ。CxxxPWRUPACK,对应CSYSPWRUPACK或CDBGPWRUPACK。

本节中描述的所有信号都是高电平有效的,因此当信号有效时均为高电平,反之则为低电平。

上电请求和响应的操作规则为:

- 调试器不能同时将

CTRL/STAT.CSYSPWRUPREQ设置为0b1,CTRL/STAT.CDBGPWRUPREQ设置为0b0。这样做造成的结果将是不可预测的(UNPREDICTABLE)。 若要开始上电过程,DP必须使

CxxPWRUPREQ信号有效。- 如果对应的电源域处于关闭状态或者处于低功耗保持状态,那么电源控制器必须在检测到

CxxxPWRUPREQ信号时对该域进行上电。当该域上电后,控制器必须使得CxxxPWRUPACK信号有效。 - 如果对应的电源域已经上电,当电源控制器检测到

CxxxPWRUPREQ信号时,调试器仍然需要将CxxxPWRUPACK信号置为有效作为响应,尽管其并未对电源域进行任何操作。

- 如果对应的电源域处于关闭状态或者处于低功耗保持状态,那么电源控制器必须在检测到

- ARM强烈建议工具仅在

CDBGPWRUPREQ和CDBGPWRUPACK有效时进行AP事务。如果CDBGPWRUPREQ或CDBGPWRUPACK处于低电平状态,任何的AP事务均可能产生错误(fault)的响应。 - DP通过将

CxxxPWRUPREQ信号置为无效以断开一个域的电源。当电源控制器接受了电源域的断电请求后,其将CxxxPWRUPACK置为无效。

注意:电源控制器将

CxxxPWRUPACK置为无效,并不意味着该域已经掉电,而仅仅是表明电源控制器已经识别并接受了对于该域的断电请求。

CxxxPWRUPACK必须默认处于低电平状态,且仅在接收了CxxxPWRUPREQ请求后转变为高电平状态。- 当检测到

CxxxPWRUPREQ信号变为无效后,除非从该域中断电会影响系统运行,电源控制器必须优雅地对电源域进行断电。举例来说,如果电源控制器有维持其他电源的请求,它可能会保持对于该域的供电。 - 在将

CxxxPWRUPREQ设置为无效以进行断电操作后,工具若要进行新的上电请求,必须等到CxxxPWRUPACK信号回到低电平状态。这一要求确保了电源控制的握手机制不被违反。

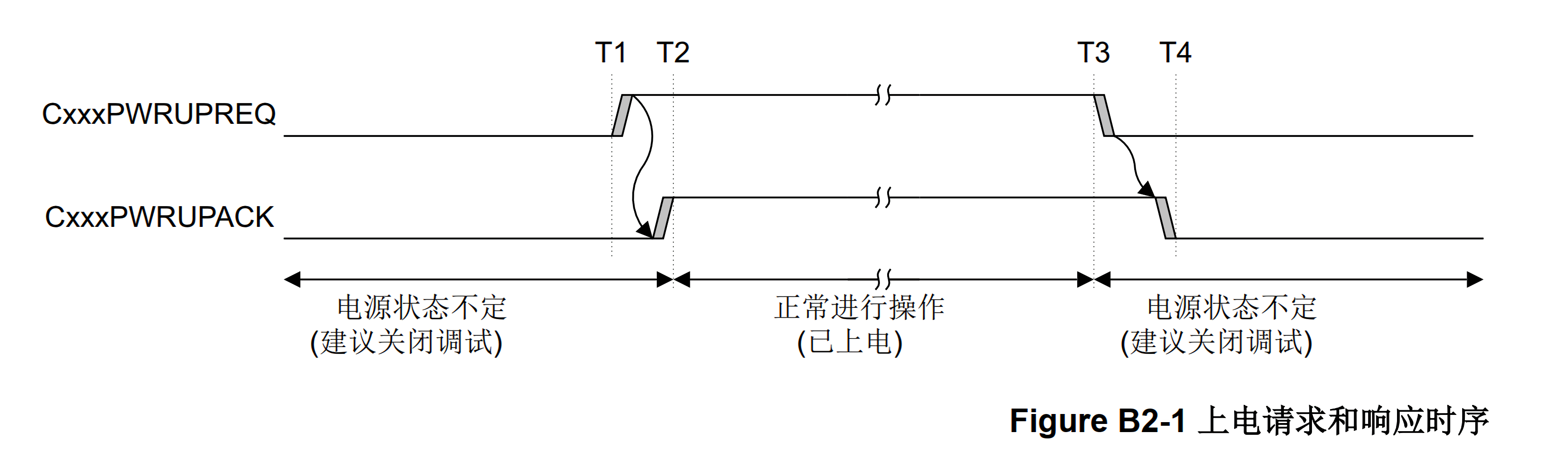

图B2-1展示了电源控制信号的时序。

注意:ARM强烈建议所有的AP事务在T2和T3之间的时间段内进行,如图B2-1所示。

模拟断电

如果DP对一个域发出了CxxxPRWUPREQ请求,而电源控制器从另外的来源收到了对于该域的冲突的请求,它必须通过完成预期握手过程来模拟对该域的断电请求,而不是真的从该域中关闭电源。这一要求确保了能够对动态上电和下电的电源域系统进行调试。

在DP发出CxxxPRWUPREQ请求后,若从其他的来源处发出以下的请求,将会造成冲突:

- 一个断电请求。

- 一个用于进入低功耗保持模式的请求,且要求关闭时钟。

对断电的模拟与应用调试有关,此时应用开发者无需考虑核心域是否真的通电和通电,因为这部分是在操作系统层面完成的。

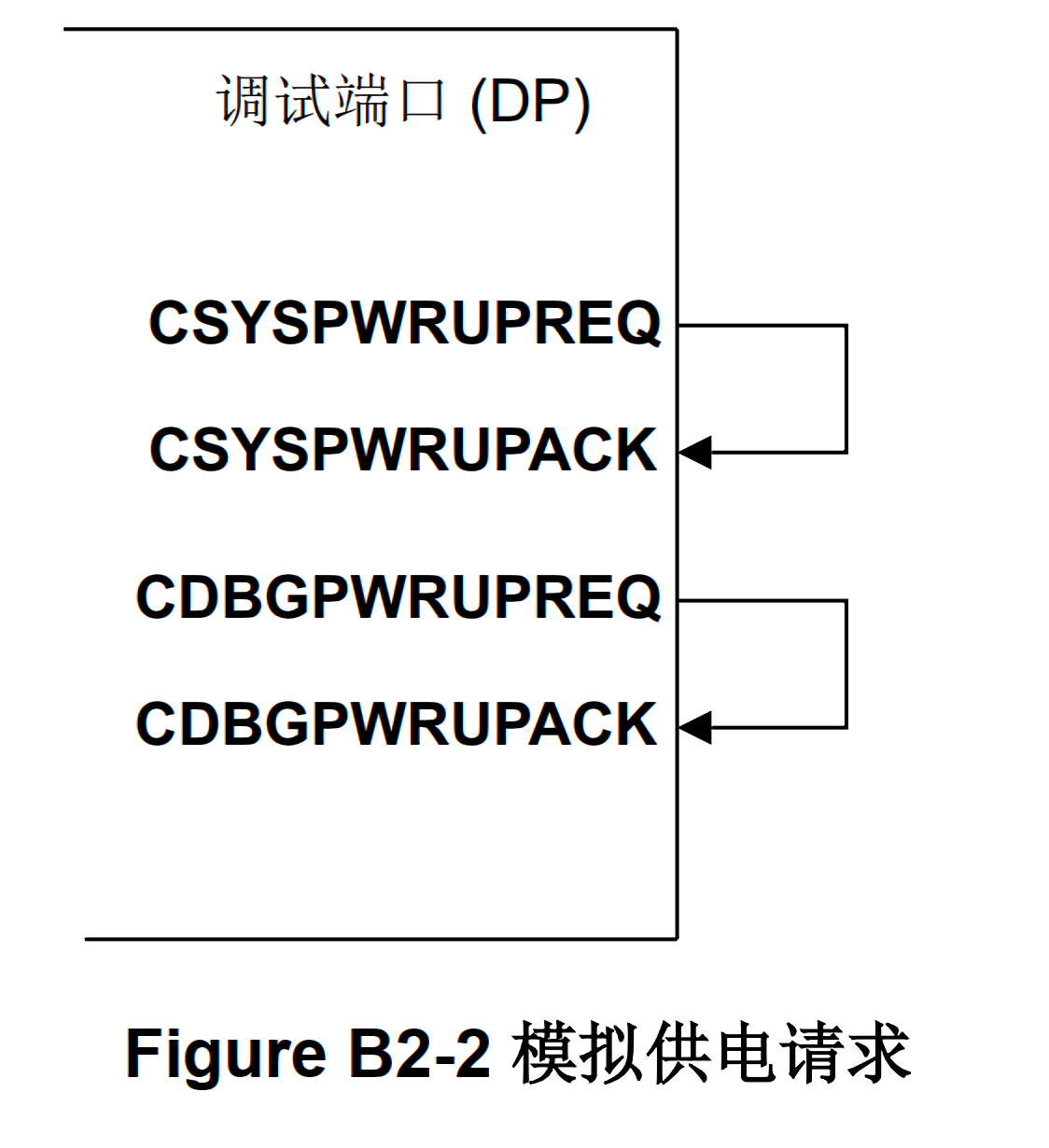

模拟电源控制

如果DP所连接的系统不支持ADIv6的电源控制模型,那么所需的信号必须被模拟或者由其他信号生成:

1.不支持ADIv6电源控制方案的系统电源控制器

为了确保DP在发出了上电或者下电请求后立即收到响应,将CxxxPRWUPACK与CxxxPRWUPREQ相连,如图B2-2所示:

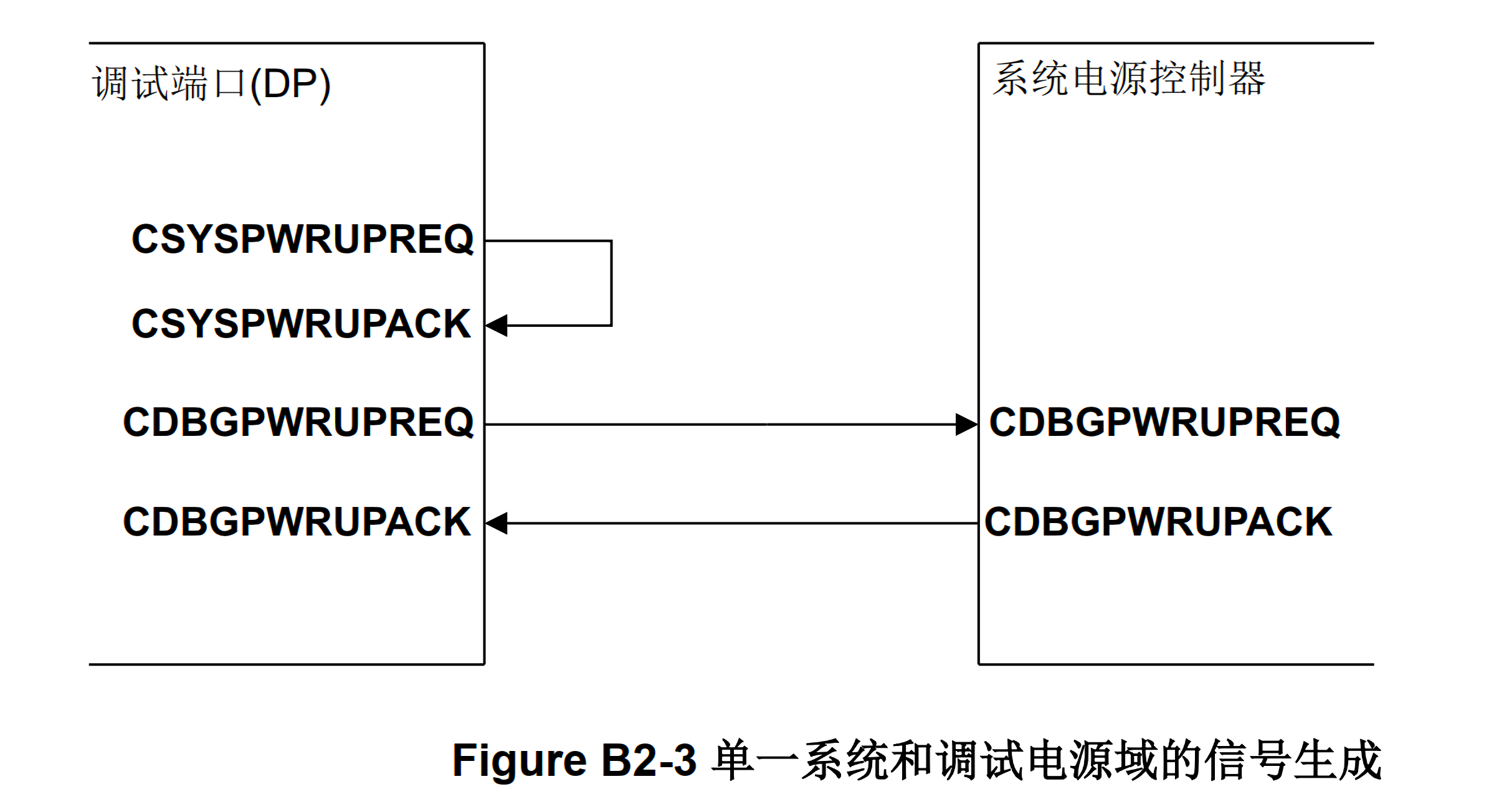

2.不支持独立电源域的系统电源控制器

如果调试电源域是系统电源域的一部分,CSYSPWRUPREQ和CDBGPWRUPREQ可以用于独立请求供电。需要正确模拟电源控制行为:

- 为了确保DP在发出系统供电请求后立即收到响应,将

CSYSPRWUPACK与CSYSPRWUPREQ相连。 - 产生合适的

CxxxPRWUPACK信号以确保DP在发出CxxxPRWUPREQ后得到正确的响应。

CxxxPWRUPACK必须按照所述的方式进行模拟。同时将CTRL/STAT.CSYSPWRUPREQ设置为0b1,CTRL/STAT.CDBGPWRUPREQ设置为0b0将会导致不可预测的(UNPREDICTABLE)系统表现。

相应的连接方式如图B2-3所示。

调试复位控制行为

DP中的CTRL/STAT寄存器提供了两个字段,用于控制调试域的复位行为,它们分别是:

CDBGRSTREQ,位[26]调试复位请求CDBGRSTREQ,位[27]调试复位响应

相关的信号提供了到系统复位控制器的连接。由这些信号控制的调试域涵盖了部分的ADI以及ADI与调试组件间的连接,例如调试总线。

DP寄存器位于DP的外部接口侧,其对应的电源域为始终开启(always-on)的电源域。因此,寄存器在任何时间下均可被驱动,用于向系统复位控制器发出复位请求。

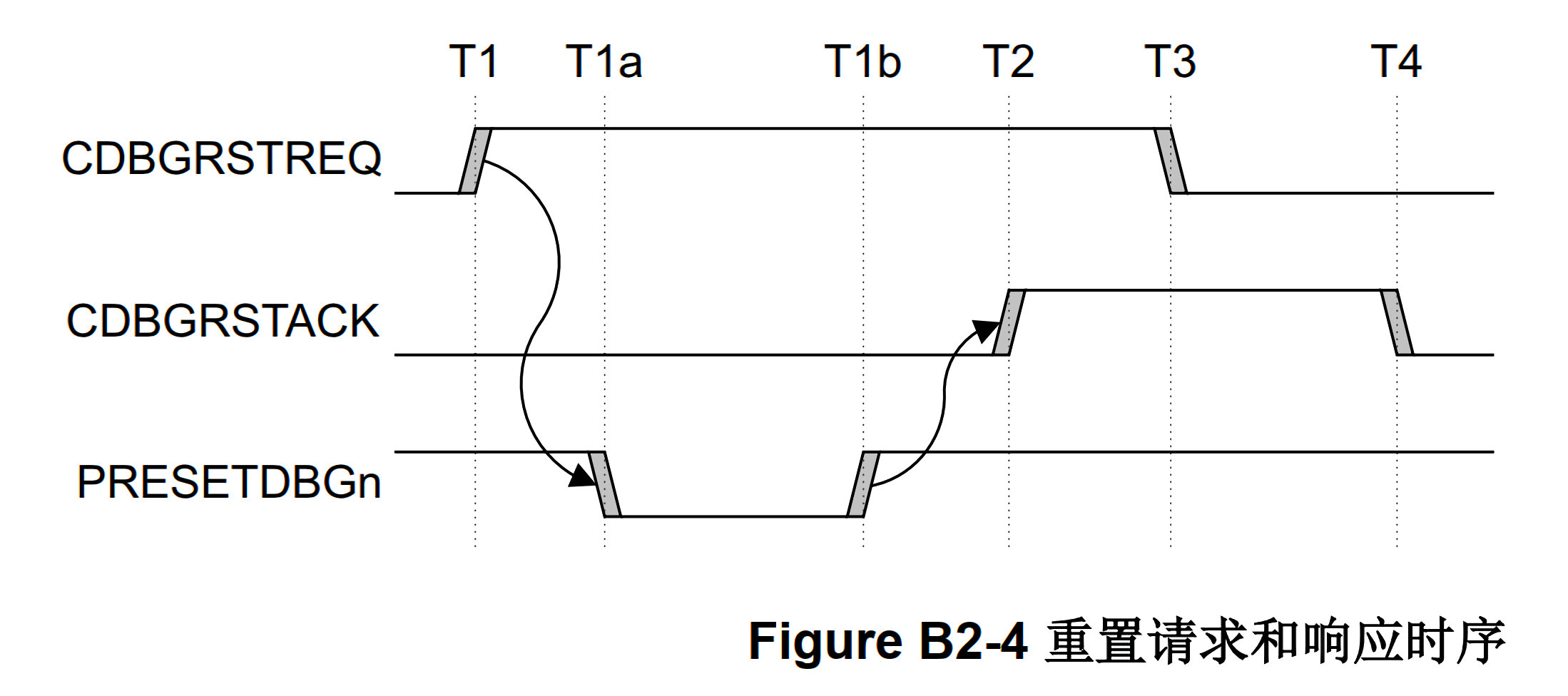

图B2-4展示了复位请求和响应的时序。

注意:在示例中使用AMBA APB信号名称并不代表必须采用AMBA APB来实现调试总线。

在图B2-4中:

- 1. 在T1时间点,调试器向

CTRL/STAT.CDBGRSTREQ写入0b1以表明要执行复位请求。调试域将在T1a和T1b之间内复位,复位操作将在T2时间点完成。该操作将重置AP寄存器和其他的AP状态。

注意:DP寄存器和DP状态将不会被重置,这些寄存器仅在上电复位时被重置。

- 2. 在T2时间点,系统复位控制器发出调试域复位完毕的响应信号。

CDBGRSTACK信号将CTRL/STAT.CDBGRSTACK位设置为0b1。 - 3. 在T3时间点,调试器检查DP的

CTRL/STAT寄存器,检查复位是否完毕。当执行完毕之后,其向CTRL/STAT.CDBGRSTREQ写入0b0以移除复位请求信号。 - 4. 在T4时间点,系统复位控制器发现

CDBGRSTREQ信号已经不再有效,因此将CDBGRSTACK置为无效。

警告:如果

CDBGRSTREQ信号在调试器发出CDBGRSTACK信号之前被移除,所导致的行为将是不可预测的(UNPREDICTABLE)。

AP调试组件同样会在调试电源域上电之后复位。

调试复位请求对发出请求时已经断电的设备没有影响。

模拟调试的复位请求

如果调试复位控制不受支持,那么:

- 由实现(IMPLEMENTATION DEFINED)来决定

CTRL/STAT.CDBGRSTREQ是可读可写(read/write)还是读为0/写忽略(RAZ/WI)。 CTRL/STAT.CDBGRSTACK的类型为读为0(RAZ)。

ARM建议将

CDBGRSTACK设置为低电平,以便调试器采用超时机制来检测是否实现了调试复位功能。

CDBGRSTREQ和CDBGRSTACK的限制

在调试复位控制行为一节中,已经展示了这些位如何驱动调试复位信号PRESETDBGn。在实际系统中,可能还有其他的复位信号与其他调试总线相关。例如,在ARM CoreSight系统中,ATRESETn重置了AMBA跟踪总线域(AMBA Trace Bus)中的所有寄存器。

注意:由实现来决定(IMPLEMENTATION DEFINED)哪些组件将被

CDBGRSTREQ请求重置。图B2-4仅仅是一个示例。不仅仅是使用PRESETDBGn的组件被重置。

由于调试逻辑可能被系统访问,如果当系统在使用调试逻辑的同时设置CDBGRSTREQ,那么实现可能会产生一些极端情况。例如,如果在事务过程中进行复位,那么可能导致系统或者软件故障。

由实现来决定(IMPLEMENTATION DEFINED)CDBGRSTREQ是否能在调试电源关闭的情况下使用。

一个系统可能包括一些由实现定义(IMPLEMENTATION DEFINED)的阻止调试复位进行的条件,例如在某些权限等级下不允许进行调试操作。

当调试复位被阻止时,CDBGRSTREQ请求信号将被忽略,CDBGRSTACK响应信号始终保持低电平。

警告:系统级的调试组件的使用必须谨慎处理。ARM建议,如果有某些可以使得调试组件在系统并不知情的情况下复位的复位系统,不要与上述的复位控制系统同时使用。ARM建议调试人员不要在非必要条件下使用调试复位请求。

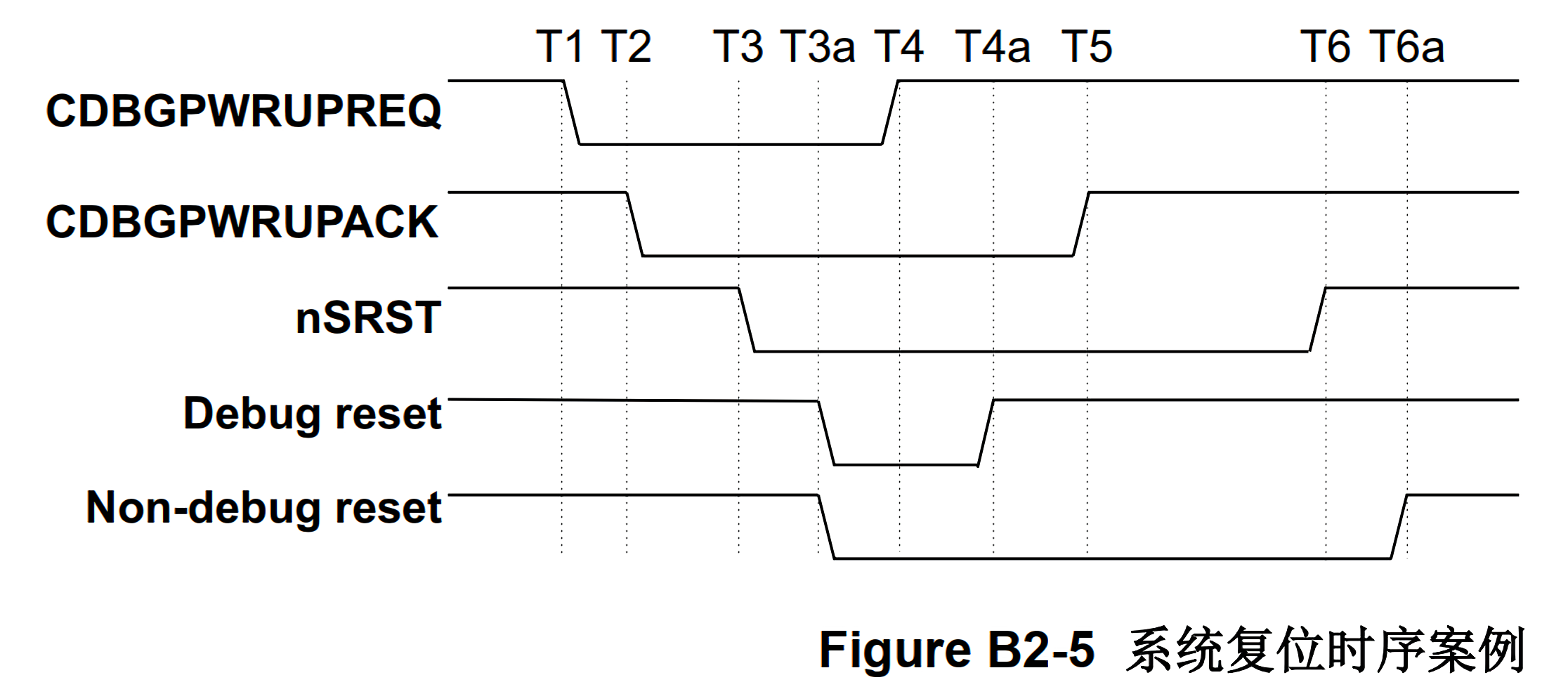

调试复位的控制行为

DP并未提供用于请求系统复位的控制位。但是,在调试器的物理接口上往往包含了一个系统复位引脚nSRST。本节描述了在nSRST引脚上请求系统复位时推荐的系统表现行为。

nSRST是一个低电平有效的引脚,可以在任何时间被置为有效或无效。不管目标系统当前状态如何,操作nSRST引脚可以使系统返回到一个已知的状态,用于启动和开始调试会话。

当nSRST有效时:

- 目标系统必须保持在一个已知的状态。

- 调试器必须能够访问目标系统的调试域。

系统复位控制的限制

调试器必须确保当nSRST有效时,DP没有正在进行中的系统访问。当nSRST有效时,调试器可以访问调试域。

nSRST对于调试域产生的影响是实现定义的(IMPLEMENTATION DEFINED)。

例如,为了安全地将目标系统退回到一个已知的状态,调试域可能同样被要求被复位。当nSRST有效时,包括调试域在内的整个系统必须被重置。不过,调试域必须在复位之后被释放,以便调试器进行访问。只有非调试域在nSRST有效时始终保持在一种复位的状态。

ARM建议调试器在nSRST开始有效之前将CTRL/STAT.CDBGPWRUPREQ设置为0b0。

- 1. 在T1时间点,调试器向

CTRL/STAT.CDBGPWRUPREQ写入0b0。 - 2. 在T2时间点,系统电源控制器对请求进行响应,并将

CTRL/STAT.CDBGPWRUPACK设置为0b0。 - 3. 在T3时间点,调试器将

nSRST引脚置为有效状态。调试域和非调试域将在T3a时间点复位,调试域将在T4a时间点完成复位。 - 4. 在T4时间点,调试器向

CTRL/STAT.CDBGPWRUPREQ写入0b1。 - 5. 在T5时间点,系统电源控制器确认了调试器的请求,并通过将

CTRL/STAT.CDBGPWRUPACK设置为0b1来表示调试域已经复位完毕。现在,调试器可以对调试域进行访问了。 - 6. 在T6时间点,调试器释放

nSRST的有效信号。非调试域的重置将在T6a时间点结束。

文中出现的术语、缩写

本部分将对文中出现的术语、缩写进行简单介绍。更详细的信息请见:ARM调试接口——术语

DP地址A、SELECT.DPBANKSEL

所有从调试器发起的AP、DP访问事务包含2个地址位,称为A[3:2]:

对于DP寄存器的访问,A[3:2]的地址位与SELECT.DPBANKSEL寄存器共同决定要访问哪个寄存器.

对于AP寄存器的访问,SELECT.ADDR寄存器和SELECT1.ADDR寄存器组合形成了64位AP地址空间中4个AP寄存器组的60位地址.地址位A[3:2]则用于选择这4个寄存器组中的其中一个.

所有的AP和DP寄存器的地址位的最低两位[1:0]为0b00.

更多信息,请见:ARM调试接口——概述。

DATA LINK DEFINED

由数据链路定义的行为。

作者注:在该文档的语境下,数据链路一般指的是JTAG-DP,SW-DP,SWJ-DP。

IMPLEMENTATION DEFINED

表示基础架构未定义该行为,但是独立的实现必须定义并归档这一行为.

Read-As-One, (RAO)

硬件实现上必须使得字段始终读出全为1的值,软件可以得到读取值全为1的保证。

这一描述适用于单个位读出为0b1,也适用于字段读出全为1的情况。

Read-As-Zero, (RAZ)

硬件实现上必须使得字段始终读出全为0的值,软件可以得到读取值全为0的保证。

这一描述适用于单个位读出为0b0,也适用于字段读出全为0的情况。

RES0

一个保留的位或字段,具有与Should-Be-Zero-or-Preserved (SBZP)相同的行为。用于寄存器描述中的字段,以及架构定义的保存于内存中的数据结构字段,例如翻译表(translation table)描述符.

有关RES0的完整信息,请见ARM调试接口——术语

Should-Be-One(SBO)

硬件必须忽略对此字段的写操作。

软件应该将字段写为全1。如果软件写入的值不是全1,那么将造成不可预料的(UNPREDICTABLE)结果。

该描述不仅适用于单个需要写为全1的位,也适用于需要写为全1的字段。

Write Ignore(WI)

硬件必须忽略对此字段的写操作。软件可以依赖写操作被忽略这一行为。这一描述适用于单个位,也适用于字段。

W1C

硬件需要为该位实现以下操作:

- 向该位写

0b1,将该位清除为0b0。 - 向该位写

0b0,对该位无影响。

UNKNOWN

UNKNOWN值不包含有效数据,其值可能随时间、指令、实现的变化而变化。

有关UNKNOWN的完整信息,请见ARM调试接口——术语

UNPREDICTABLE

对于ARM处理器,“不可预测的(UNPREDICTABLE)”意味着该行为不能被依赖。

有关UNPREDICTABLE的完整信息,请见ARM调试接口——术语