SWD协议解析(待完成)

引言

目前在中文社区中有关SWD协议的内容较少.本文旨在介绍(翻译)SWD协议的具体内容与实现.完整的标准文档可以在ARM网站上下载到.

具体的标准为Arm® Debug Interface Architecture Specification 目前的版本是ADIv6.0

基本信息

该节中包含了SWD协议中常用到的一些概念.它们是:

- SWD协议版本

- 基本传输流程

- 比特序(Bit order)

- 奇偶校验(Parity)

- 线路周转(Line turnaround)

- 空闲周期(Idle cycles)

- 多点局限性(Limitations of multi-drop)

SWD协议版本

这部分简要了解即可.

SWD协议v1:

点对点架构(point-to-point),支持单一主机(Host)和单一设备(Device)的连接.主机可以通过建立其他的连接以连接到其他设备.其存在着一些缺点:

- 多个设备在物理连接上存在一定不便

- 增加了设备所需的外部引脚数,同时对芯片内部的Die也有要求

- 调试多种平台对于单种控制器的集成要求较高

总的来讲就是同时调试不同平台的设备比较麻烦.

SWD协议2旨在解决多个串行调试设备之间的连接问题,但同时引入了限制最大连接速度的trade off.

SWD协议v2:

多点架构(multi-drop),具有以下特性:

- 主机仅需两条线即可与多个设备同时通信

- 允许的有效连接数不设限(仅受本身电气特性限制)

- 在最大程度上支持向后兼容(点对点架构本来就是多点结构的一部分)

- 在没有选中设备时,允许设备完全关闭电源

- 防止多个设备对总线的竞争操作,支持总线被主动驱动为高电平或低电平,进而保持较高的最大时钟速度

- 在多点连接中,允许接入不支持SWD协议的设备

需要注意的是,在SWD的第二个版本中需要实现对休眠状态的支持,可能存在与第一个版本之间的兼容问题

For an SWJ-DP implementation, JTAG is selected on a powerup reset. Selecting SWD bypasses the dormant state, and subsequent operation is compatible with SWD protocol version 1.

For an SW-DP implementation of SWD protocol version 2, the dormant state is selected on a powerup reset, meaning the start-up state differs from a start-up with SWD protocol version 1. After SWD operation is selected, operation is compatible with SWD protocol version 1.

比特序

即数据传输的顺序.在SWD中所有数据的比特序为最低有效位优先(LSB),即先传输低位数据,再传输高位数据.

举例来说,对于

OK的ACK响应,其数据为0b001,先传输最低位1,再传输0,最后传输最高位0.

空闲周期(Idle cycles)

顾名思义,SWD的传输闲置时的状态称作空闲周期.

主机通过把SWDCLK时钟线拉低来代表空闲时期.

线路周转(Line turnaround)

ARM SWD采用的是一条双向的数据连接线(SWDIO),为了防止主机与设备对于数据连接线的竞争,在传输方向发生变化时,需要一个周转时间(周转期),在此期间主机与设备均不驱动数据线,数据线的电平状态不定(x).

周转期的时间长度由

DLCR寄存器的TURNROUND位域控制. 默认是一个时钟周期.

Tips: 采用高采样率时钟时,线路周转可以提供引脚延迟(pad delay)

基本传输流程

Arm SWD接口使用一个双向数据连接线(SWDIO)一个时钟线(SWDCLK)来传输数据.

基本传输流程可分为三步:数据包请求(Packet request),ACK响应(Acknowledge response),以及数据传输(Data transfer)

- 数据包请求(报头)

调试器主机向调试端口(DP,Debug Port)发出一个请求.这里的DP指的是接收请求的设备的调试端口. - ACK响应

当DP接收到主机的数据包请求时,向主机发出响应.一般地,当响应为"OK"时才会进行接下来的数据传输. - 数据传输

3.1 数据传输方向:

1. 主机->设备(HOST->TARGET),写数据(WDATA)

2. 设备->主机(TARGET->HOST),读数据(RDATA)

3.2 数据传输的开始条件:

- 在传输过程中已经接收到OK的ACK响应.

- 被调试设备的控制/状态(CTRL/STAT)寄存器中

ORUNDETECT标志位被设置为0b1,即开启的状态.

ORUNDETECT标志位代表了超限检测(?)(Overrun detection)模式的开启状态.该模式允许调试器主机与设备之间进行长时间和高吞吐量的连接(high latency and high throughput).在上电之后该功能默认禁用,即设置为

0b0.

需要注意的是,如果上述的ORUNDETECT标志位被设置,那么在所有的响应中(包括WAIT和FAULT),数据传输阶段是始终被要求存在的.

3.3 数据传输过程

- 主机发出请求,且设备接收到了该请求

- 在经过一个周转期后,设备立即发出ACK响应

- 如果有数据等待发送,在作出ACK响应且满足数据传输的开始条件后,这些数据可能会等待/不等待周转期,然后继续发送(具体的等待条件如下)

- 对于写入请求,在ACK阶段和数据传输阶段有一个周转期.当WDATA传输完毕后,没有周转期,主机继续驱动总线.

- 对于读取请求,具体表现与写入请求相反.在ACK阶段和数据传输阶段没有周转期.当RDATA传输完毕后,存在一个周转期,随后主机继续驱动总线.

3.4 数据传输完毕后的操作

当数据传输完毕后,主机需要进行下列选项中的任一操作:

- 发送起始位,立即开始一轮新的SWD请求

- 以空闲时期驱动SWD接口,直到需要进行新一轮的请求

- 如果主机需要停止SWD时钟,那么至少应驱动8个空闲周期的时钟,然后再停止时钟.

奇偶校验

在所有的数据传输过程中,都会使用偶校验(Even Parity).做法是在数据传输完后加上一个偶校验位.具体的校验过程如下:

- 对于数据包请求(数据包请求),在四位的

APnDP,RnW和A[2:3]上进行. - 对于数据传输阶段(

WDATA和RDATA),在WDATA[0:31]或RDATA[0:31]上进行

偶校验:传输的数据中为

1的个数为偶数,结果为0,否则为1

当调试器主机在进行读取操作时,读取到连续的36Bit数据的数据组成为:

Bits 0-2对应ACK[0:2]Bits 3-34对应RDATA[0:31]Bit 35对应奇偶校验位

进行奇偶校验时,ACK[0:2]不包含在奇偶校验的校验范围内,即主机应该只对Bits 3-34进行奇偶校验,将结果与Bit 35比较是否一致.

写入

TARGETSEL发生奇偶检验错误时会取消对设备的选中.更多与寄存器相关的操作与相应详见手册.

读取数据过程中,如果发生奇偶校验错误,主机可能需要重新读取数据

设备ID(Target ID)

原本在手册中,这是作为多点架构的局限性(Limitations of multi-drop)引入的,但是这又是SWD中很重要的一个概念,因此单独起一节来讲.

每个设备需要用一个包含4bit的实例ID(instance ID)来作为唯一的设备ID(target ID),用来在连接过程中将自己与其他设备区分开来.

上电之后,由于所有的设备都会被主机选中,故如果不预先使用设备ID将设备进行选中,主机将无法与设备进行通信.

多点架构的局限性*(Limitations of multi-drop)

设备自动连接到一个多点架构的SWD系统需要满足,或者说有这些局限:

- 主机需要预先知道系统中具有的设备,且在设备连接之前进行配置

- 主机将尝试发送给每个设备一个目标选择命令,用以尝试自动检测设备.对于主机而言,需要在合适的时间内迭代所有受支持的设备.

由于以上局限的存在,调试主机无法无缝连接到先前从未连接的设备,除非主动向调试主机提供这类设备的目标ID.

此外,SWD v2还对设备作出了一些要求,具体见手册.

SWD协议操作

本节将介绍SWD协议的具体操作.

术语

本节包含SWD协议中的常用术语

- StarT : 一个单独的起始位,其值为

0b1 - Stop : 一个单独的停止位,其值为

0b0 - Parity : 一个单独的奇偶校验位

- Trn : 周转.参见线路周转一节.

注意:下面示例的所有周转期均使用一个时钟周期

- Park : 一个单独的位.在进入周转期之前,主机必须把暂存位(Park Bit)拉高.由于SWD接口的上拉很弱,为了保证设备读取到的值为

0b1,需要将其拉高. - APnDP : 一个单独的位,指示要操作"调试端口"(Debug Port)还是操作"访问端口寄存器"(Access Port Access register).值为

0b0表示DPACC操作,即操作"调试端口", 值0b1表示APACC操作,即操作"访问端口寄存器". - RnW : 一个单独的位,指示操作是读取还是写入.值

0b0表示写入,值0b1表示读取. A[2:3] : 两个位,给出了

DP或AP寄存器的位域地址.- 对于

DPACC操作,要寻址的寄存器取决于A[3:2]的值.如果A[3:2]的值为0b01,则寻址地址为SELECT寄存器中DPBANKSEL的值. - 对于

APACC操作,要寻址的寄存器取决于A[3:2]和SELECT寄存器中的{APSEL,APBANKSEL}

- 对于

注意,我们这里写作A[2:3]是为了表明其在传输时是低位(LSB)优先的.

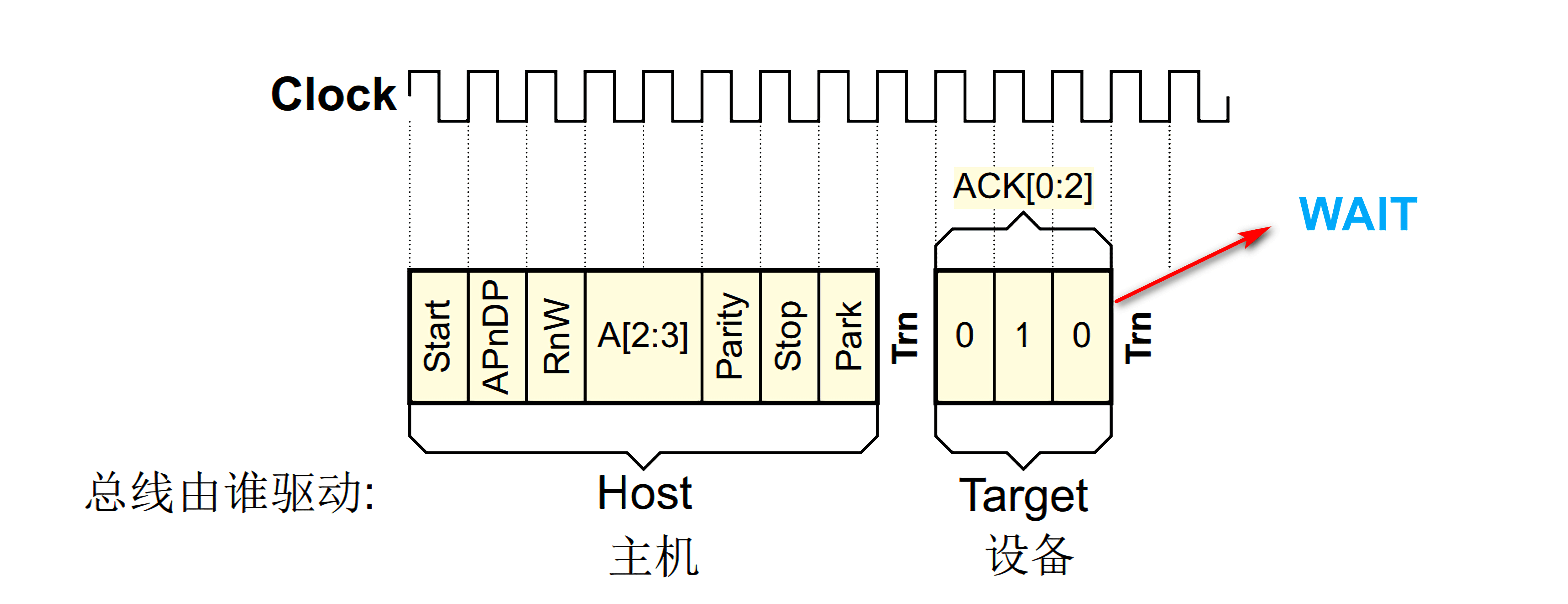

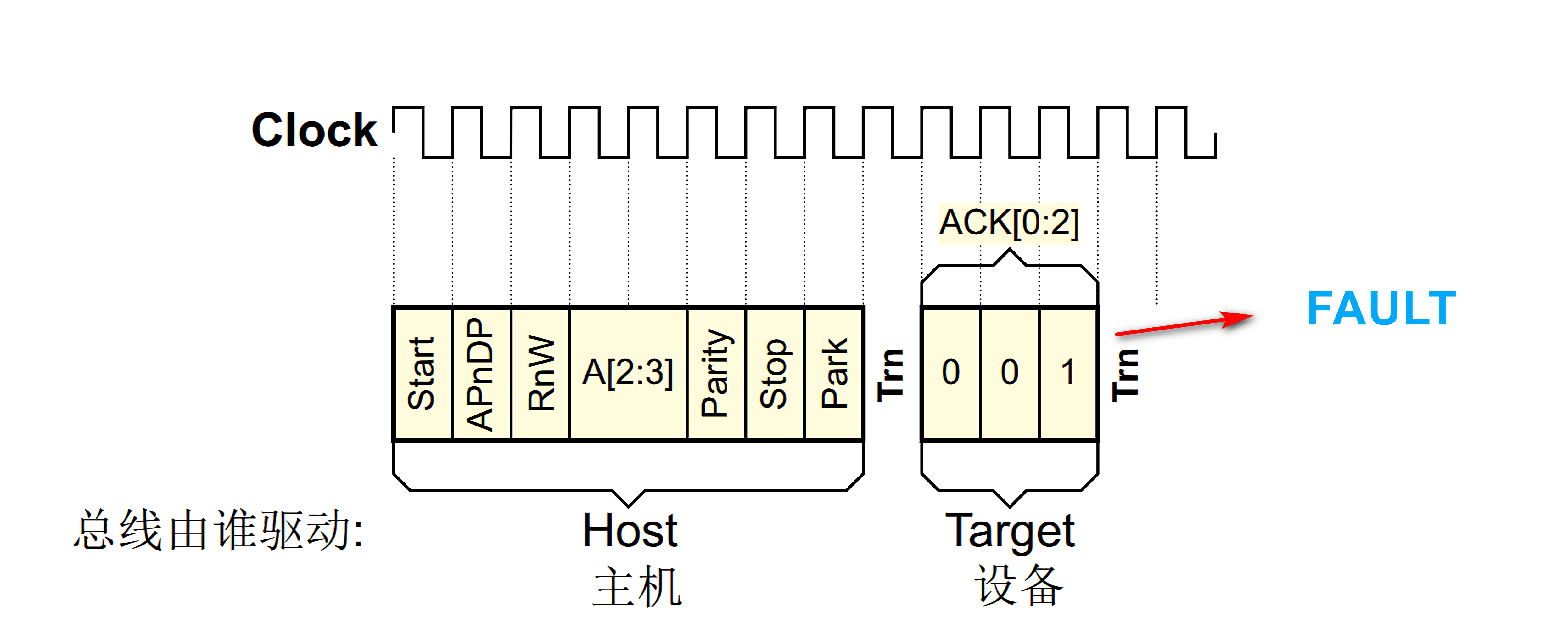

- ACK[0:2] : 三位的值,表示设备对主机请求的响应状态,下表展示了可能的状态值:

| ACK[0:2]编码 | 代表的响应 | 可能出现的情况 |

|---|---|---|

| 0b100 | OK | 成功读取/写入操作的响应 |

| 0b010 | WAIT | 等待读取/写入操作的响应 |

| 0b001 | FAULT | 发生错误的响应 |

注意这里的字节序,对于OK响应,其最低位为1.

- WDATA[0:31] 32位的写入数据,方向由主机到设备

这里的字节序同样是低位(LSB)优先的,故这里写作WDATA[0:31]

- RDATA[0:31] 32位的读取数据,方向由设备到主机.

这里的字节序同样是低位(LSB)优先的,故这里写作RDATA[0:31]

协议过程综述

协议遵循上文所述的基本传输流程,在下面的具体传输流程中不再复叙传输流程.

协议操作1:成功写入操作(OK响应)

当设备收到一个写入请求数据包时,如果设备已经准备好进行数据传输且无错误发生,那么完整的传输流程如下:

主机在接收到OK的ACK响应后,经过一个周转期后必须立即开始数据的传输,在数据传输完毕之后没有任何的周转期,以便于主机立即驱动线路以进行下一轮操作.

对于写入操作,写入DP寄存器和AP寄存器的操作是相同的.当数据传输阶段完毕后,对于DP值的写入立即作用到DP寄存器上,而对于AP值的写入可以先作用到缓冲区上,稍后进行写入.(详见手册)

这里所述的写入不适用于对TARGETSEL寄存器的写入操作,具体见下文连接与总线重置序列一节.

协议操作2:成功读取操作(OK响应)

与写入类似,当设备收到一个读取请求数据包时,如果设备已经准备好进行数据传输且无错误发生,那么完整的传输流程如下:

可以看出,在第一阶段和第二阶段之间有一个周转期.在数据传输完毕后也有一个周转期.而在ACK阶段和数据传输阶段之间无周转期,因为这时的数据均由设备驱动,不需要转换方向.

对于AP寄存器的读取请求将被"投递"(Post)出去,这也就意味着请求结果将在下一次传输过程中返回(注:本次的返回的数据是不确定的,你需要忽略它).这个结果可能是对于另一个AP寄存器的读取结果,也可能是对DP中RDBUFF(读取缓冲区)寄存器的读取结果.

如果需要进行一系列有关AP的读取操作,调试器仅需对RDBUFF寄存器进行一次读取即可,具体步骤如下:

- 对于第一次的

AP读取请求,返回的结果是不确定的,调试器必须忽略该结果. - 对于下一次的

AP读取请求,如果成功读取,将访问上一次的读取结果. - 可以重复发出任意数量的

AP读取请求.返回的结果与上面两条所述的类似,对于最后一次发出的请求,返回的结果是倒数第二次的读取结果. - 随后,调试器可以读取

DP上RDBUFF寄存器以获得最后一次的AP读取结果.

为了让调试器能从总线错误中恢复,在读取完AP寄存器的下一轮传输可以读取任意的DP寄存器.如果这里的“下一轮传输”读取的是除了RDBUFF以外的DP寄存器,那么在接下来的AP寄存器读取操作或者RDBUFF读取操作中将会返回第一次的AP寄存器读取结果.

当然,如果尝试在“下一轮传输”是对AP/DP寄存器的写入或者对RDBUFF的读取,返回的值是不确定的,并且第一次的AP寄存器读取结果将会丢失.

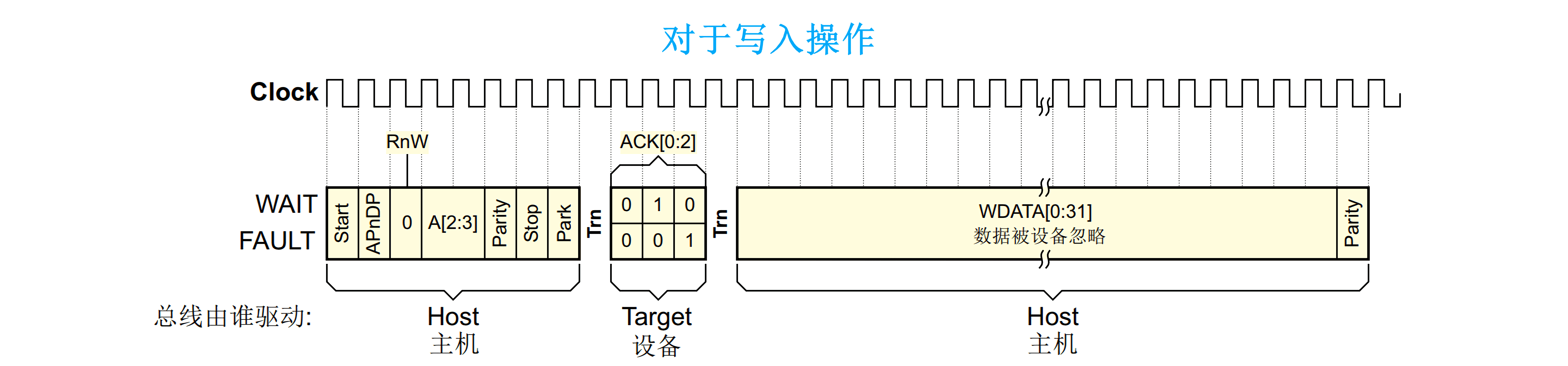

协议操作3: 写入和读取中的等待操作(WAIT响应)

如果设备正忙,无法立即响应主机的读取或写入请求,其需要发出一个WAIT响应,其仅由两部分组成:

你可以其看作是成功写入操作中缺少数据传输阶段并且更改了ACK后的结果.

注意:如果启用了超限检测,那么仍然需要数据传输阶段的参与,详见后面章节的有关内容.

一般地,设备可能发出WAIT响应的情况可能有以下几种:

- 先前对于

AP/DP寄存器的访问操作还未完成. - 新的请求是

AP读取请求,但是先前的AP请求尚不可用.

然而,存在一些例外情况,以下的请求不能采取WAIT响应:

- 对于

DPIDR寄存器的读取操作. - 对于

CTRL/STAT寄存器的读取操作. - 对于

ABORT寄存器的写入操作.

对于调试器而言,在收到WAIT响应后,其将多次重试发送相同的请求以便尽快处理数据.调试器可能在较长时间内尝试多次请求操作,以便适应较差的连接质量和较慢的被调试设备.如果始终得不到OK响应,调试器可以尝试写入ABORT寄存器的DAPABORT标志位,表明其希望中止传输.

在某些实现上,

AP可能无法终止传输,但是当其收到abort的操作请求时必须释放DP的接口.

当接收到WAIT响应后,调试器可以尝试进行ABORT操作,进而访问调试系统的其他部分.

协议操作4: 写入和读取中发生错误的操作(FAULT响应)

发生错误时的操作与等待操作类似,从传输序列上看仅仅是ACK响应上存在不同:

与等待操作类似,如果启用了超限检测,同样需要具备一个数据传输阶段.

在一般情况下,调试端口对于以下的请求不应该发出FAULT响应:

- 对

DPIDR寄存器进行读取,这是一个只读寄存器. - 对

CTRL/STAT寄存器进行读取,这是一个可读可写寄存器. - 对

ABORT寄存器进行写入,这是一个只写寄存器.

如果你尝试进行一些不寻常的操作(例如试着对一个只写寄存器进行读取操作),当CTRL/STAT寄存器的sticky标志位被启用(设置为0b1),那么调试端口将发出一个FAULT响应.

SWD协议能够借助FAULT响应保持同步.对于调试器而言,其可能传输由数据块构成的数据流,并在数据块的末尾检查

CTRL/STAT寄存器的情况.

协议错误响应

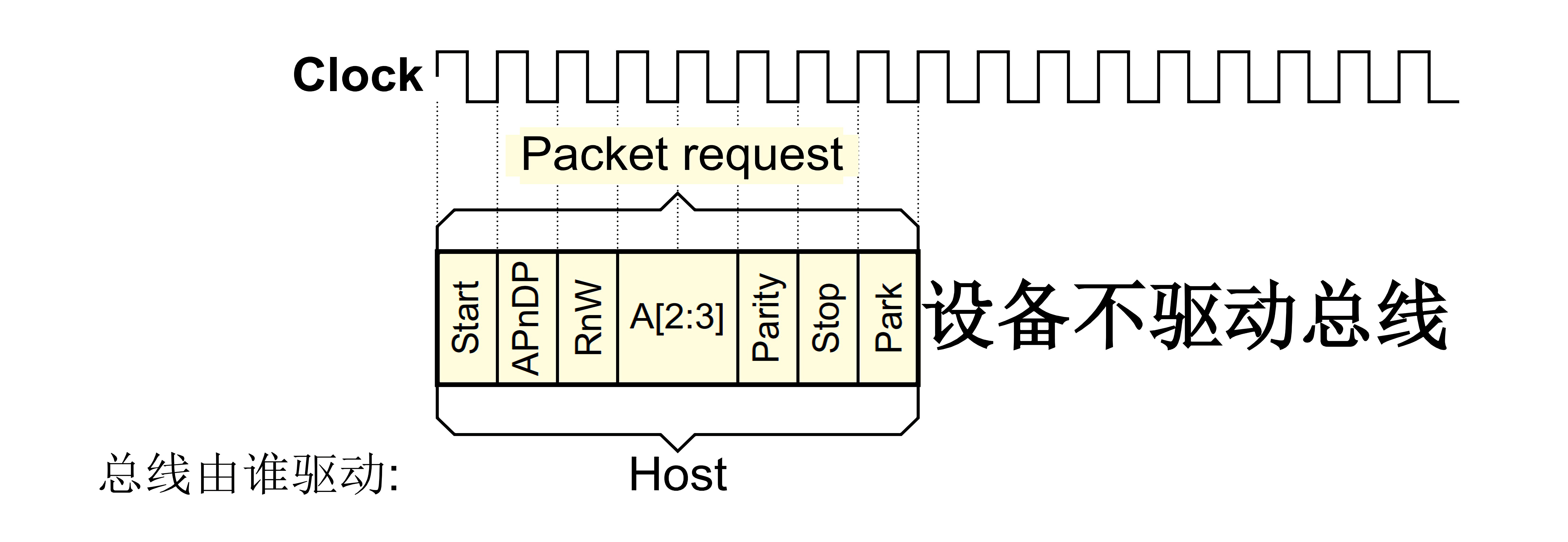

当下面的情况发生时,标志着协议出现了错误:

- 在第一阶段(数据包请求阶段)奇偶检验位校验失败

- 停止位不为0b0.

- 暂存位(Park Bit)不为0b1.

DLCR中的TURNROUND错误,即周转期设置不当.

注意:在WDATA的传输过程中奇偶校验位校验失败不属于协议错误.调试端口可以通过其他方式来表明发生了这一错误.

设备对于协议错误的响应

当协议出现错误时,设备将不返回任何数据,且不会驱动总线:

如果启用了超限检测,需要等待数据传输阶段结束才可以进入协议错误状态.如果不启用,设备将立即进入协议错误状态.

如果实现了SWD v2协议,调试端口不会返回对于

TARGETSEL寄存器的访问请求.

当发生协议错误时,设备具有以下行为:

- 如果检测到有效的对

DPIDR寄存器的读取操作,那么由设备实现来决定(IMPLEMENTATION DEFINED)是否要让设备退出协议错误状态,并给出一个OK响应. - 如果检测到有效的数据包请求,但不是对

DPIDR寄存器的读取操作,或者设备检测到其自身定义的额外一定数量(IMPLEMENTATION DEFINED)的协议错误,设备将进入锁定(lockout)状态.

关于这两种状态,还有一些规则:

- 如果设备无法在读取DPIDR寄存器时退出协议错误状态,则协议错误和锁定状态是等效的.

- 当总线重置时,设备必须退出错误状态

- 设备仅在总线重置时退出锁定状态.

- 如果设备实现了SWD v2协议,并且在总线重置后立即发生了一次协议错误,那么设备将直接进入锁定状态.如果在总线重置后的第一次传输过程中传输正常,没有发生协议错误,那么此后在发生一定次数(IMPLEMENTATION DEFINED)的协议错误后,设备才进入锁定状态.

主机对于协议错误的响应

如果主机一直没有收到预期中的目标响应,那么至少在整个数据传输阶段,主机都不应驱动总线.在此之后,主机可以尝试进行线路的重置.

不推荐的操作:主机在进行线路重置前,可以尝试对

DPDIR寄存器进行读取,如上文中所说的,这时候设备或许能够响应该请求并退出协议错误状态.*:如果原始的操作是写入,且发生了协议错误,我们可以认为这次写入操作没有进行.如果原始的操作是读取,这可能造成对

AP寄存器的读取操作,尽管这种情况发生的概率很低,但是由于这种操作是通过流水线(pipelined)来进行的,我们必须考虑这种可能的存在.

迟滞超限行为(Sticky overrun behavior)

正如前面所说的,当设备未处理完上一个数据包请求时,就已经收到一个新的请求,它将会响应一个WAIT的ACK.

但是,如果启用了超限检测功能,当继续收到更多的数据包时,将产生一个FAULT响应.

当启用了超限检测功能时,

CTRL/STAT寄存器中的STICKYORUN标志位会被置为0b1.此外,产生FAULT响应、发生协议错误或者总线重置均会使该标志位置位.

当启用了超限检测功能时,在进行WALT或者FAULT响应之后,必须包含完整的数据传输阶段:

- 如果传输是读取读取数据,那么数据传输阶段中出现的数据是不确定的.设备不应该驱动总线,主机也不应该检查数据的奇偶校验位.

- 如果传输阶段是写入数据,那么这些写入数据将被设备忽略

下图展示了这两种不同的传输行为:

写入数据缓存(write buffering)

调试端口可以实现写缓冲区,这样在其他的事务还未处理完毕时也能接受写入操作.在这种实现中,如果其可以对请求进行写缓冲区的写操作,那么将对主机发出OK响应.注意,此时的OK请求仅代表请求被接受,并不意味先前所有的写入操作均已经完成.

未完成的事务的类型以及最大数量由实现决定(IMPLEMENTATION DEFINED).调试端口的实现需要保证所有的访问是按照顺序进行操作的.举例来说,如果调试端口仅缓冲对于AP寄存器的写入操作且当写缓冲区已经有缓冲的数据时,必须要暂缓对于DP寄存器的写操作以保证顺序执行写操作.

尽管写入操作被接受写入缓冲区中,但在此后它有可能被丢弃.当缓冲区的数据被丢弃时,CTRL/STAT寄存器中的WDATAERR标志位被置位.出现以下的情况时,可能会发生丢弃的现象:

- 先前的操作过程中将

sticky标志位置位. 尝试读取

DPIDR,DPIDR1,CTRL/STAT寄存器.因为这些寄存器是即时响应的,这些请求不能被缓存.当尝试这样做时,调试端口的行为应为:- 立即执行对

DPIDR,DPIDR1,CTRL/STAT寄存器的访问操作. - 丢弃缓存的所有写入操作,否则将导致写入操作的无序执行.

- 将

WDATAERR标志位置位.

-尝试对ABORT寄存器进行写入.该请求不能被缓存.

- 立即执行对

当你进行一系列的AP写入操作时,如果发现WDATAERR标志位被置位,你可能无法借助ACK响应来确定具体哪个操作是失败的,不过你可以借助其他方法来找到它.例如,可以使用内存访问端口的自动地址递增(AddrInc)功能,通过读取传输地址(Transfer Address Register,TAR)寄存器,可以找到最后一次成功操作的地址.

欲进行以下操作时,应当先清空写缓冲区:

- 任何对于

AP的读取操作. - 除了读取

DPIDR,DPIDR1,CTRL/STAT寄存器或者写入ABORT寄存器以外的任何有关DP的操作.

当写缓冲区非空时,尝试上述操作将使得调试端口发出WAIT响应.

如果启用了推送验证或推送比较功能,那么对于AP写入事务将转换为对AP的读取.这类事务的处理方式与其他的AP写入操作相同.详见手册.

在进行一系列的AP读取操作后,如果要立即对DPIDR,DPIDR1,CTRL/STAT寄存器进行读取或者对ABORT寄存器进行写入,必须先进行一些允许的暂缓操作,让写缓冲区先清空,再进行相关的DP寄存器的访问操作.否则,WDATAERR标志位将被置位,且将导致已经缓冲的数据丢失.

当执行完AP写入操作后,以下的行为不需要额外的暂缓操作:

- AP读取操作

- 本身就可以进行暂缓的写入操作,例如对

SELECT寄存器的写入

通常情况下,额外的暂缓操作是能够避免的.

小结:设备响应

本章节展示了设备对于AP事务以及DP事务的响应.

DP事务

对于DP事务,要访问的寄存器取决于:

A[3:2]的值- 当

A[3:2]的值为0b01时,取决于SELECT寄存器中DPBANKSEL的值

下面的两个表分别展示了对DP进行读取和写入时设备的响应.

发生FAULT的情况不包含在上述的表中,具体的请见下文中的内容

AP事务

对于AP事务,要访问的寄存器由以下两者共同决定:

A[3:2]的值SELECT寄存器中的{APSEL,APBANKSEL}.

更多有关于AP寄存器的操作请查看手册.

下面的两个表分别展示了对AP进行读取时设备的响应,以及写入时得到正确校验WDATA的设备响应.

发生FAULT的情况不包含在上述的表中,具体的请见下文中的内容

不包含在汇总表中的FAULT情况

有两种FAULT情况不包含在上述的汇总表中,它们分别是:

协议错误

如果发生了协议错误,设备根本不会响应请求.当主机准备接受ACK响应时,其会发现线路并未被驱动.详见协议错误响应章节.写操作时WDATA奇偶校验位校验失败

`DP`相关事务的ACK响应是在奇偶校验之前发送的,正如表4-2所示.当奇偶校验位校验失败时,`CTRL/STAT`的`WDATAERR`标志位被置位.

小结:主机行为

调试器主机的每一项传输操作都从传输请求报头开始,在上一个章节中我们已经总结了主机可能发出的所有请求以及设备对各个请求的响应.

对于调试器主机而言,每次发出一个请求报头后,均期望从设备处得到一个3位的ACK响应.在下文的表中,总结了当设备收到ACK响应后应该执行的操作.

对于SWD v2协议,此表不适用于对

TARGETSEL寄存器的写操作.见下文连接与线路重置序列章节.

SWD接口

SWD协议采用串行同步接口,该接口包含一个双向数据信号以及一个时钟信号.

本章节主要讲述物理SWD接口.

总线接口

对于调试主机和被调试设备,共用一个双向数据引脚SWDIO.

SWD接口是同步的,需要一个时钟引脚SWCLK.

当设备需要对SWDIO进行采样时,应在SWCLK的上升沿执行采样.当设备对SWDIO进行驱动或者停止驱动时,信号在SWCLK的上升沿发生变化.

时钟信号可以从被调试设备获取并引出,或者由调试主机提供.该时钟信号被主机用作生成和采样数据的参考,因此设备不需要对其进行任何的过采样(over sampling).

主机和设备均可将总线驱动为高电平、低电平或者高阻态.接口必须能够接受因为失去同步而带来的短时间竞争现象.

SWCLK时钟不需要与任何的系统时钟进行同步,包括调试逻辑时钟(debug logic clock).当调试端口闲置时,可以停止SWCLK时钟.参见前文SWD协议基本信息一节.

线路上拉(pull up)

为了确保在主机和设备均没有驱动总线时,总线处在一个确定的状态,需要在设备处进行100KΩ的上拉.这种上拉仅仅是为了维持线路的状态,当总线被驱动为低电平并被释放时,上拉电阻会使得总线恢复为高电平(尽管这种过程要耗费一定的时钟周期).

上拉可以防止在没有设备连接时,主机检测到错误的信号.此外应该尽量具有较高的上拉,以便减少主机主动拉低线路时对设备造成的电流消耗.

每当线路被驱动为低电平时,在设备处都有少量电流流失.如果设备需要使用低功耗模式,且SWD接口长时间连接,主机应该将线路保持为高电平状态或者进行复位,直到需要使用到SWD接口为止.

连接与线路重置序列

对于调试器而言,需要使用一个线路重置序列,以确保SWD接口在进行热插拔时不会造成意外的串行连接.使用一个线路重置序列可以确保调试器主机与设备的正确同步.

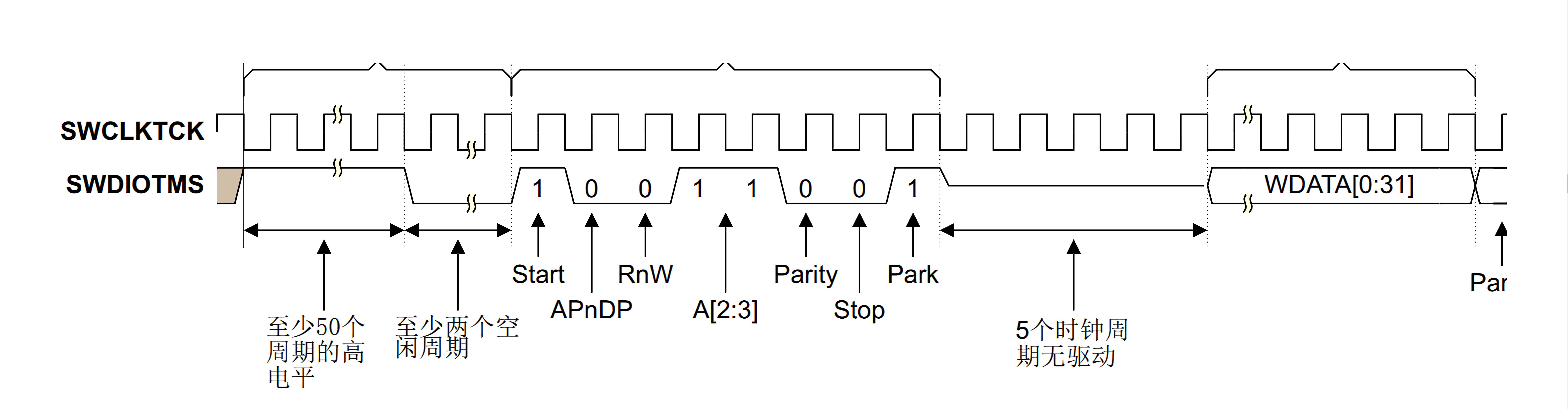

SWD接口并不包含所谓的复位信号线.通过将数据信号线保持高电平,持续至少50个周期,之后保持至少两个的空闲周期,即可实现线路复位.下图展示了线路复位以及随后对于DPIDR寄存器的读取时序:

首次连接到设备时,需要进行线路重置.此外,发生协议错误后可能需要进行线路重置.

当进行完线路重置后:

DCLR寄存器被重置SELECT寄存器的DPBANKSEL位于必须设置为0x0

注意:其余的寄存器仅在上电时进行重置.

在等待数据报头时,如果设备检测到复位序列,即数据信号保持至少50个时钟周期的高电平,随后至少有2个空闲周期,则其必须进入复位状态.在其他时候检测到50个周期的高电平信号,是否要进入复位状态由实现来决定(IMPLEMENTATION DEFINED).

当设备进入复位状态时,只有部分传输操作有效:

- 对

DPIDR寄存器的读取操作.该操作将使得设备退出复位状态. - 接收到SWD与JTAG的切换序列(如果已经实现了的话)

- 对

TARGETSEL寄存器的写入操作(如果实现了SWD v2协议).如果此项操作选中了设备,接口将仍然保持复位状态.

注意:只有在进入复位状态后立即对

TARGETSEL寄存器进行写入才能选中或者取消选中设备.参见下文的SWD v2协议目标设备的选择.

上面提到的传输操作均可被新的一次总线重置打断.如果在复位状态下进行其他的传输操作,造成的结果是不可预知的.

如果主机在尝试读取DPIDR寄存器时没有收到预期的响应,那么主机应当再次尝试进行线路重置.这可能是因为设备处于某种状态,例如,设备将线路重置序列当做是数据传输阶段中的数据序列,这样就不能识别到有效的线路重置信号.这样,设备将视线路重置序列为协议错误,需要进行新的一轮线路重置.

如果开启了超限检测功能,线路重置将会使得 CTRL/STAT中的STICKYORUN标志位置位.

SWD v2协议之目标设备的选择序列

这里所说的"目标设备的选择序列"是用于复位之后在多个连接到的设备中选择合适的设备所采用的传输序列.具体的操作流程如下:

- 进行线路重置.

- 将需要选中的设备的ID写入到地址为

0xC的TARGETSEL寄存器中,同时忽略设备返回的结果. - 读取地址为

0x0的DPIDR寄存器,以验证设备是否被成功选中.

在对TARGETSEL寄存器进行写入后,必须读取DPIDR寄存器或者进行复位操作.如果读取DPIDR寄存器的响应不正确或者没有响应,主机必须重新发送目标设备的选择序列.

当设备接收到线路重置序列时,默认进入选中状态.此后在接收到TARGETSEL的写入序列,且其代表的选中设备不为自身时,设备取消选中.

当设备处于取消选中的状态时,设备将忽略所有的访问操作,并且不能驱动总线.对于调试器主机而言,要选择或取消选择设备,必须在总线重置之后立即对TARGETSEL进行写入,在其他时间进行TARGETSEL的写入所导致的行为都是不可预测的.

如果在传输过程中设备遭遇协议错误,它将被取消选择.具体来说,它不会响应接下来对于DPIDR寄存器的读取请求.

更多有关

TARGETSEL寄存器的写入、响应以及其他行为信息,请参阅手册的B1-43节.

在写入TARGETSEL寄存器的数据传输阶段,如果奇偶校验位校验失败,并不会导致CTRL/STAT中的WDATAERR标志位被被置位,但是设备仍然会以协议错误对待该行为.

对TARGETSEL寄存器的访问不会受到CTRL/STAT寄存器中{STICKYERR, STICKYCMP,STICKYORUN}位域状态的影响.

SWD v2协议必须支持休眠操作,请参阅手册中的有关部分.